## Defect-Based Testing of LTS Digital Circuits

*Arun Antony* Joseph

#### **Graduation Committee:**

Chairman: prof.dr.ir. A. J. Mouthaan

Secretary: prof.dr.ir. A. J. Mouthaan Univ. Twente, EWI

Promoter: prof.dr.ir. T. Krol Univ. Twente, EWI

Assistant promoter: dr.ir. H. G. Kerkhoff Univ. Twente, EWI Referee: prof.dr.ir. J. Flokstra Univ. Twente, TNW

Members: prof.dr. J. Schmitz Univ. Twente, EWI

prof.dr. H. Wallinga Univ. Twente, EWI prof.dr. R. A. M. Wolters prof.dr. H. Rogalla Univ. Twente, TNW

prof.dr. C. I. M. Beenakker TU Delft

The research presented in this thesis has been carried out at the Testable Design and Testing of Nanosystems group (TDT), Mesa+ Institute for Nanotechnology, University of Twente, The Netherlands.

Title: Defect-Based Testing of LTS Digital Circuits

Author: Arun Joseph ISBN: 90-365-2362-1

© Arun Joseph, Enschede, The Netherlands, 2006.

No part of this work may be reproduced by print, photocopy or any other means without the prior permission in writing from the author.

Email: Arun.Joseph@gmx.net

Cover Design by Yosep Sugiarto, Corner Stone Production, The Netherlands.

Printed by Wöhrmann Print Service, Zutphen, The Netherlands.

# DEFECT-BASED TESTING OF LTS DIGITAL CIRCUITS

#### **DISSERTATION**

to obtain

the doctor's degree at the University of Twente,

on the authority of the rector magnificus,

prof.dr. W.H.M. Zijm,

on account of the decision of the graduation committee,

to be publicly defended

on Wednesday 10<sup>th</sup> May 2006 at 15.00

by

Arun Antony Joseph Born on 31<sup>st</sup> May 1978 in Cochin, India This dissertation has been approved by promoter:

prof.dr.ir. T. Krol

and assistant promoter:

dr.ir. H. G. Kerkhoff

I am the Lord, and there is no other; There is no God besides Me. I will gird you, though you have not known Me, That they may know from the rising of the sun to its setting That there is none besides Me. I am the Lord, and there is no other (Is 45:5-6)

The fool has said in his heart, "There is no God." (Ps 14:1; Ps 53:1)

- The Bible

## **Contents**

| List o  | f Tables                                               | xi   |

|---------|--------------------------------------------------------|------|

| List o  | f Figures                                              | xiii |

| Chapter | r1 Introduction                                        | 1    |

| 1.1 En  | nerging High-Speed Applications                        | 2    |

|         | per-Conductor Electronics (SCE)                        |      |

|         | oblem Definition and Chosen Approach                   |      |

|         | utline of the Thesis                                   |      |

| 1.5 Re  | ferences                                               | 9    |

| Chapter | r2 Superconductor Electronics for Digital Applications | 11   |

| 2.1 Int | roduction                                              | 12   |

| 2.2 Jos | sephson Junctions                                      |      |

| 2.      | 2.1 Junction Models                                    |      |

|         | sephson Junction Circuits                              |      |

| 2.4 De  | esign and Implementation of RSFQ Circuits              |      |

|         | 4.1 An RSFQ DFF                                        |      |

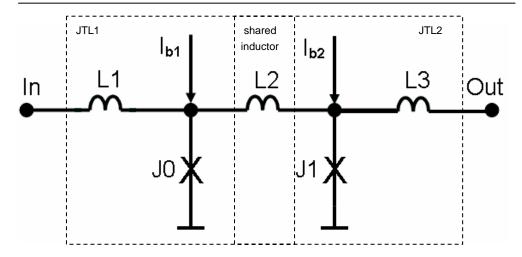

| 2.      | 4.2 Josephson Transmission Line (JTL)                  |      |

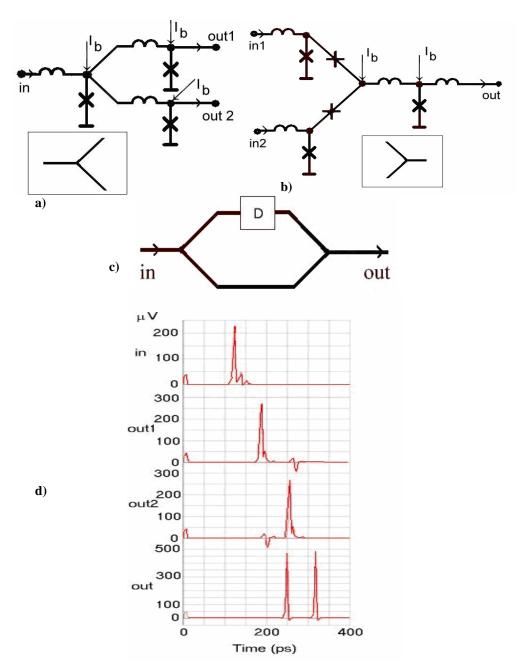

|         | 4.3 RSFQ Splitter and Merger                           |      |

|         | Ivantages and Disadvantages of RSFQ Circuits           |      |

|         | onclusions.                                            |      |

| 2.7 Re  | ferences                                               | 28   |

| Chapte  | er 3 Test Techniques for VLSI RSFQ Circuits            | 31   |

| 3.1 Int | roduction                                              | 32   |

| 3.2 Me  | ethodologies for IC testing                            | 32   |

| 3.      | 2.1 Structural and Defect-Based Testing                | 33   |

| ٠.      | 2.2 Design for Testability                             |      |

| 3.3 Di  | agnosis of the IC Fabrication Process                  | 35   |

| 3.4 De  | etermination of Random Defect Distribution             | 38   |

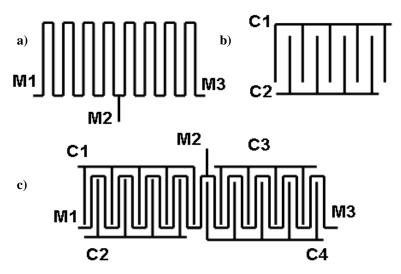

| 3.      | 4.1 Intra-layer Shorts and Opens                       | 38   |

| 3.      | 4.2 Interlayer shorts                                  |      |

| 3.      | 4.3 Step-coverage problem                              |      |

|         | 4.4 Contact (-via) problems                            |      |

|         | ocess Analysis of Superconductor Electronics (SCE)     |      |

|         | T for RSFQ Circuits                                    |      |

|         | onclusions.                                            |      |

| 2 8 Pa  | ferences                                               | 52   |

viii Contents

| Cha  | pter 4 LTS    | RSFQ Processes and Associated Defects                                  | . 55 |

|------|---------------|------------------------------------------------------------------------|------|

|      |               |                                                                        |      |

|      |               | es for the Realisation of RSFQ Circuits                                |      |

| 4.3  | The JeSEF N   | b Process                                                              |      |

|      | 4.3.1         | Probable Defects in the JeSEF Process                                  |      |

|      | 4.3.2         | Structures for the Detection of Probable Defects in the JeSEF Process. |      |

| 4.4  | The HYPRES    | S Nb Process                                                           |      |

|      | 4.4.1         | Probable Defects in the HYPRES Process.                                |      |

|      | 4.4.2         | New Test Structures for the HYPRES Process                             |      |

|      |               | Structures for Junction Measurements                                   |      |

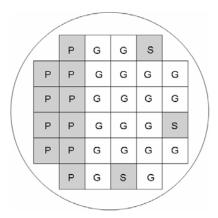

|      |               | entation of Test Chips for Defect Data                                 |      |

|      |               | n of Defects in an LTS RSFQ Process                                    |      |

|      |               |                                                                        |      |

| 4.9  | References    |                                                                        | 93   |

| Cha  | pter 5 Strue  | ctural Testing: Defect Analysis of the RSFQ Processes                  | .97  |

|      | -             |                                                                        |      |

|      |               | t Techniques at Room Temperature (RT)                                  |      |

|      |               | he JeSEF Process                                                       |      |

| 3.3  | 5.3.1         | Graphical Analysis of Defect Data                                      |      |

|      | 5.3.2         | Statistical Analysis of Defect Data                                    |      |

| 5 1  |               | he HYPRES Process                                                      |      |

|      |               | t Techniques at Low Temperatures                                       |      |

|      |               | recliniques at Low Temperatures                                        |      |

|      |               |                                                                        |      |

| 3.1  | References    |                                                                        | 133  |

| Cha  | pter 6 Defe   | ct-Based Testing of LTS RSFQ Circuits                                  | 137  |

| 6.1  | Introduction. |                                                                        | 138  |

|      |               | n RSFQ circuit testing                                                 |      |

|      |               | on a JeSEF DFF                                                         |      |

|      | 6.3.1         | I <sub>DDX</sub> Testing                                               |      |

|      | 6.3.2         | Digital Structural Testing                                             |      |

| 6.4  | Defect-Based  | 1 Testing of a HYPRES DFF                                              |      |

|      |               | ng of Defects                                                          |      |

|      |               | of the RSFQ DFF                                                        |      |

| 0.0  | 6.6.1         | Limitations of the Modelling Approach                                  |      |

| 6.7  |               | bgy for the Verification of Fault Models                               |      |

|      | 6.7.1         | Proposed DfT Scheme for Model Verification                             |      |

|      | 6.7.2         | Defect Insertion in the RSFQ DFF.                                      |      |

|      | 6.7.3         | Limitations of the Methodology                                         |      |

| 6.8  |               | on of a Test Scheme for Verification                                   |      |

|      |               | on or a rest periodic for verification                                 |      |

| 6.10 |               | es                                                                     |      |

|      |               |                                                                        |      |

**Contents** ix

| Chapter 7 Conclusions                     | 169 |

|-------------------------------------------|-----|

| 7.1 Summary of the Thesis and Conclusions | 170 |

| 7.2 Original Contributions of this Work   | 172 |

| 7.3 Recommendations for Future Work       | 173 |

| 7.4 Concluding Remarks                    | 174 |

| Abbreviations                             | 175 |

| List of publications                      | 177 |

| Acknowledgements                          | 179 |

#### **List of Tables**

| Chapter 4 LTS RSFQ Processes and Associated Defects                           |    |

|-------------------------------------------------------------------------------|----|

| Table 4.1: Mask Definitions of the JeSEF Process                              | 50 |

| Table 4.2: Trilayer Characteristics6                                          |    |

| Table 4.3: List of predicted defect locations in the JeSEF Process            |    |

| Table 4.4: List of the most probable defect locations in the JeSEF Process    |    |

| Table 4.5: Mask Definitions of the HYPRES Process                             |    |

| Table 4.6: Sub-steps in the HYPRES Nb Process                                 | 12 |

| Table 4.7: List of predicted defect locations in the HYPRES process           | 16 |

| Table 4.8: Examples of cross-sectional analysis on the HYPRES cell libraries7 | 19 |

| Table 4.9: Classification of defects in an LTS RSFQ Process9                  | 2  |

|                                                                               |    |

| Chapter 5 Structural Testing: Defect Analysis of the PSEO Processes           |    |

| Chapter 5 Structural Testing: Defect Analysis of the RSFQ Processes           |    |

| Table 5.1: Results showing the details of defect data from a JeSEF Wafer10    |    |

| Table 5.2: Summarised statistics of the JeSEF_Jan02 Wafer 117510              |    |

| Table 5.3: Overall statistical results of the JeSEF Process from 4 wafers     |    |

| Table 5.4: Statistics of measurement data of the HYPRES Wafer 66511           |    |

| Table 5.5: Summary of the measurement results of HYPRES wafer #66511          |    |

| Table 5.6: Statistical results of the HYPRES process from 8 wafers11          |    |

| Table 5.7: Ranking of the defect-prone locations in the HYPRES Process        | 21 |

|                                                                               |    |

| Chapter 6 Defect-Based Testing of LTS RSFQ Circuits                           |    |

| Table 6.1: Two different testing approaches of an RSFQ DFF14                  | 16 |

| Table 6.2: Ranking of the defect-prone areas in the HYPRES process            |    |

| Table 6.3: Details of the defect-prone locations in the DFF circuit.          |    |

| Table 6.4: Simulation results of the defect-induced HYPRES DFF circuit        |    |

| Table 6.5: Details of defect insertion by layout modification                 |    |

### List of Figures

**Chapter 1 Introduction**

| Figure 1.1: Micropho                                                                                                                                                                                                                                                                                            | tograph of the Flux-1 RSFQ microprocessor (Courtesy: NGST)3 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Chapter 2 Su                                                                                                                                                                                                                                                                                                    | perconductor Electronics for Digital Applications           |

| Figure 2.2: Circuit m<br>Figure 2.3: Piece-wis<br>Figure 2.4: Protocol<br>Figure 2.5: Mealy di<br>Figure 2.6: An RSFQ<br>Figure 2.7: Layout o<br>Figure 2.8: Circuit so                                                                                                                                         | c of a Josephson junction                                   |

| Chapter 3 Te                                                                                                                                                                                                                                                                                                    | st Techniques for VLSI RSFQ Circuits                        |

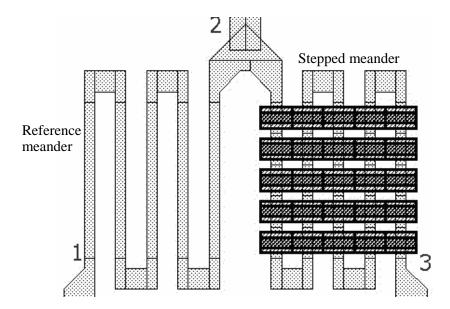

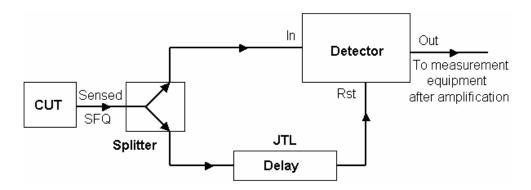

| Figure 3.2: Structure Figure 3.3: Cross-sec Figure 3.4: Structure Figure 3.5: Increase Figure 3.6: Structure Figure 3.7: "Van der Figure 3.8: Analysis Figure 3.9: Block dia Figure 3.10: Circuit & Figure 3.11: Simulat Figure 3.12: Schema Figure 3.13: Insertion Figure 3.14: Insertion Figure 3.15: Simulat | p showing the presence of defects in a process              |

xiv List of Figures

| Chapter 4        | LIS RSFQ Processes and Associated Defects                                |      |

|------------------|--------------------------------------------------------------------------|------|

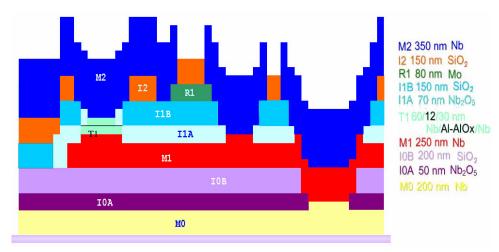

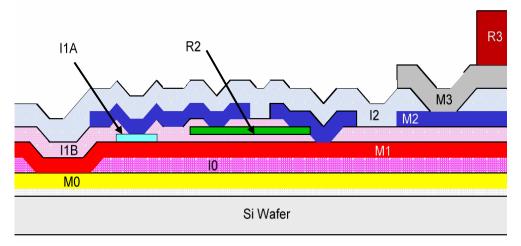

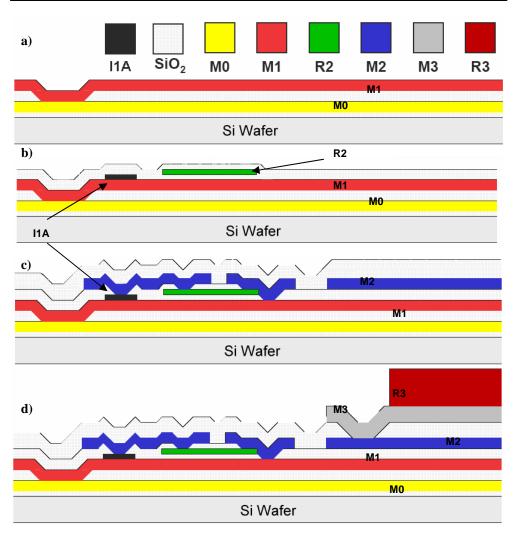

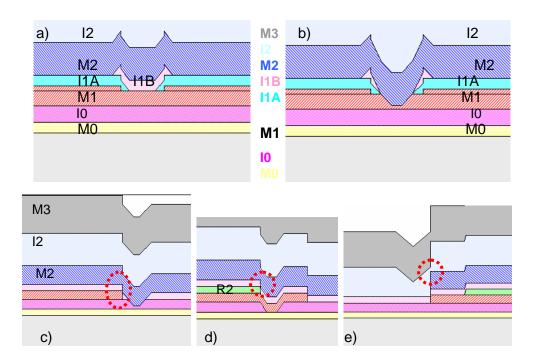

| Figure 4.1: Cro  | ss section of the JeSEF Nb process                                       | 57   |

|                  | cess flow of the JeSEF Nb process                                        |      |

|                  | M analysis on a JeSEF sample chip.                                       |      |

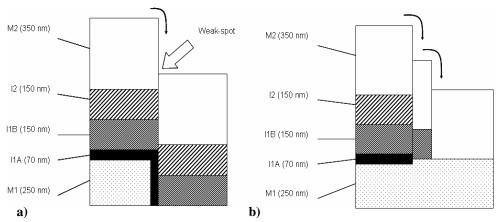

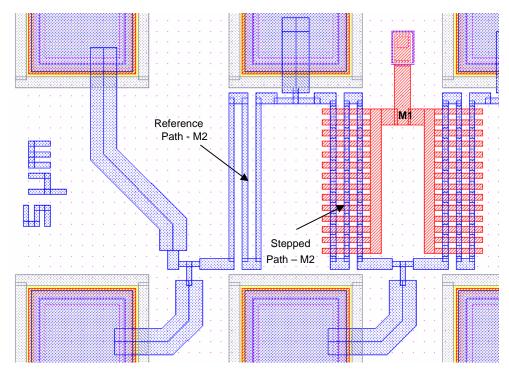

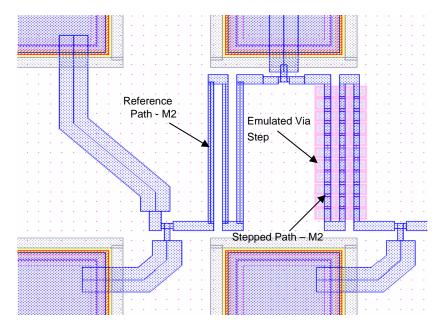

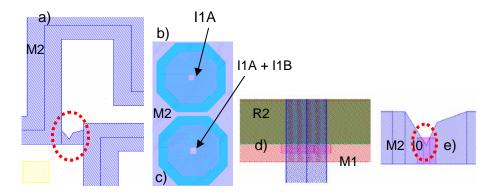

| Figure 4.4: Cros | ss sectional examples of the M2 steps in the JeSEF process               | 64   |

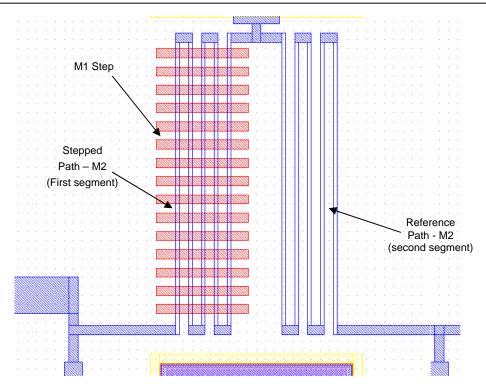

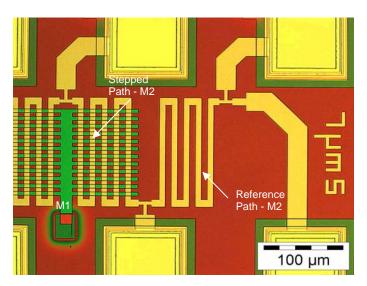

| Figure 4.5: Lay  | out of the test structure to detect opens in M2 over an M1 layer edge    | 67   |

| Figure 4.6: Lay  | out of the structure for step-coverage problem over a via                | 67   |

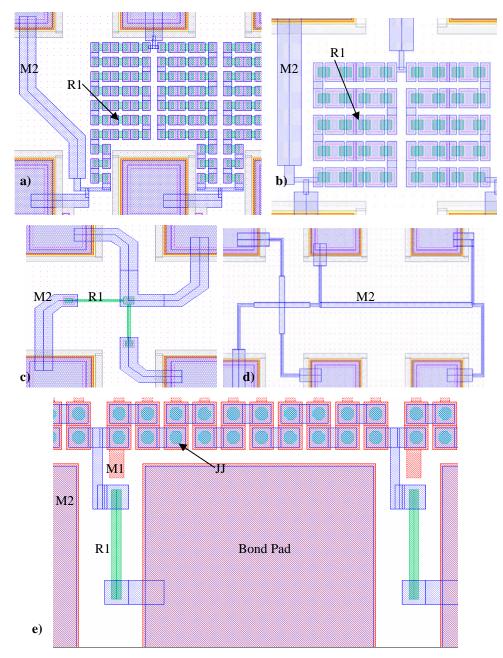

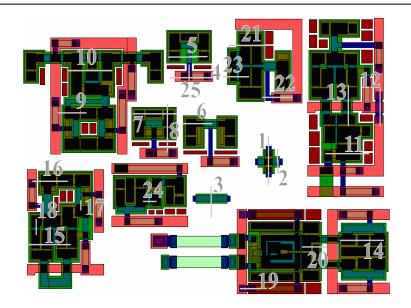

|                  | s of various test structures developed in the JeSEF process              |      |

|                  | ss Section of the HYPRES Nb process.                                     |      |

| Figure 4.9: Prod | cess flow of the HYPRES Nb process                                       | 73   |

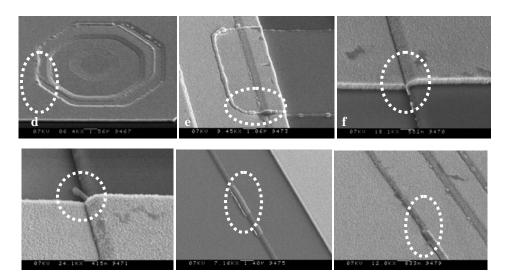

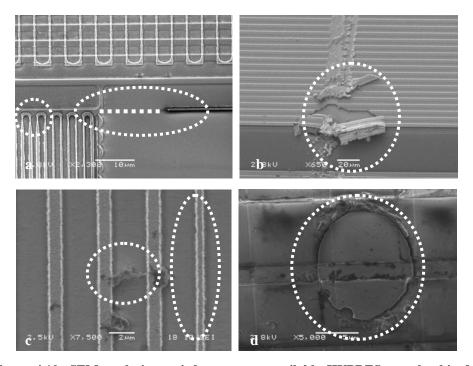

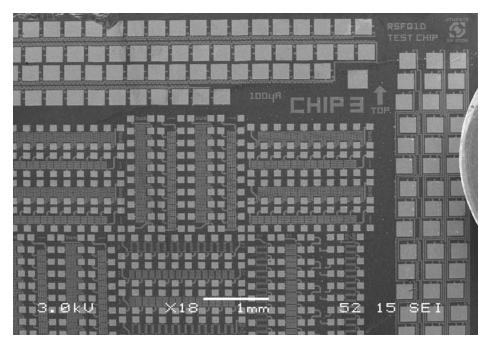

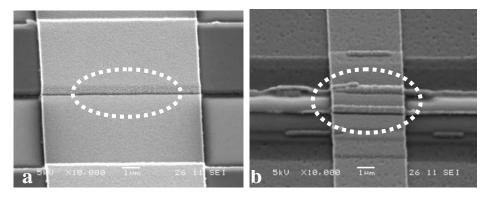

| Figure 4.10: SE  | M analysis on HYPRES sample chip                                         | 75   |

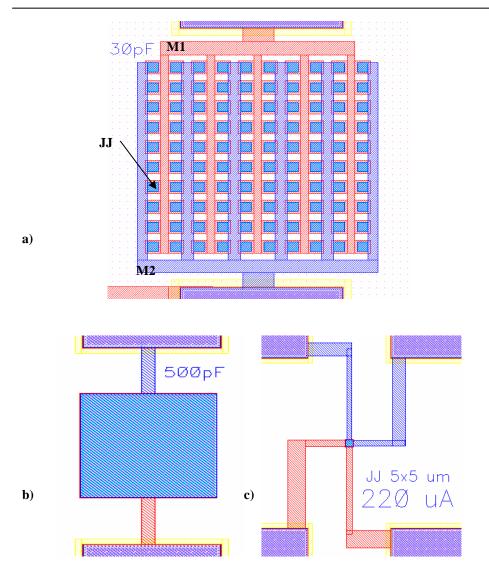

| Figure 4.11: Lil | brary cells designed in the HYPRES process                               | 78   |

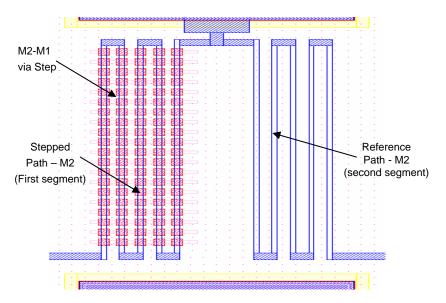

| Figure 4.12: La  | yout of the adapted test structure for opens in M2 over an M1 layer edge | e82  |

| Figure 4.13: La  | yout of the adapted test structure for opens in M2 over an M2-M1 via     | 82   |

| Figure 4.14: Pa  | rts of structures developed for the HYPRES Nb process                    | 83   |

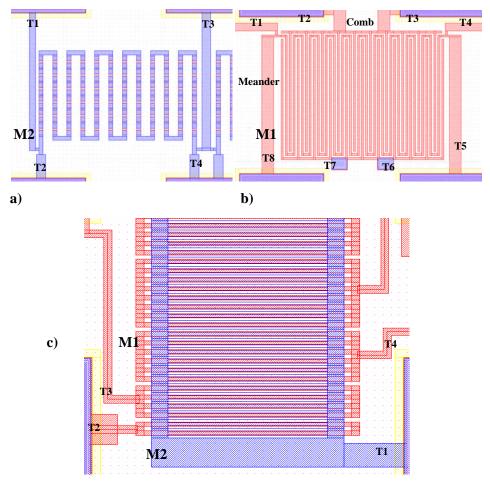

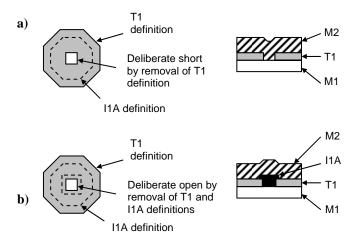

| Figure 4.15: Ins | sertion of defects deliberately into a JJ                                | 84   |

| Figure 4.16: Sp  | ecial room temperature structures for the detection of defects in a JJ   | 86   |

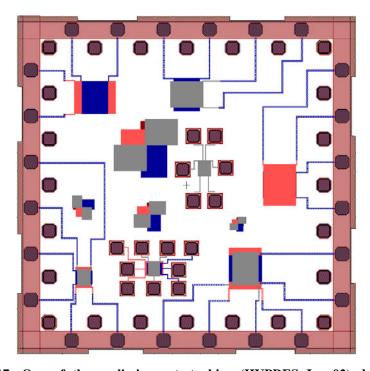

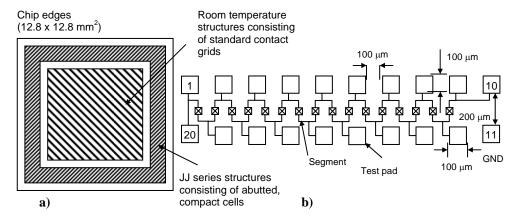

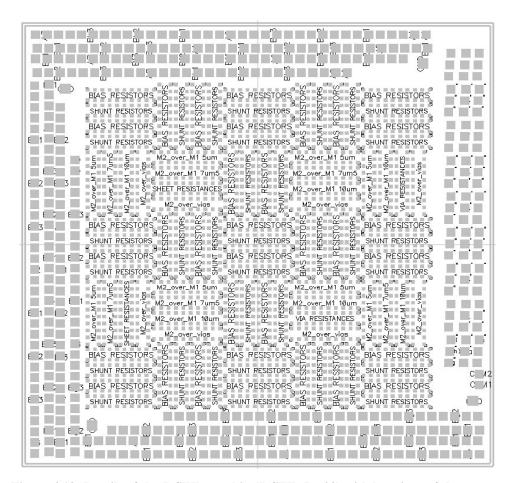

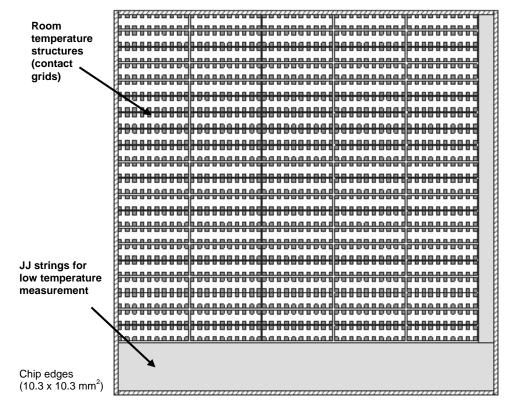

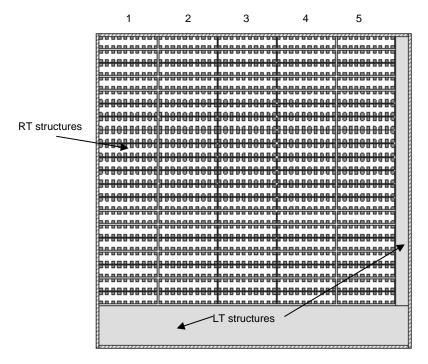

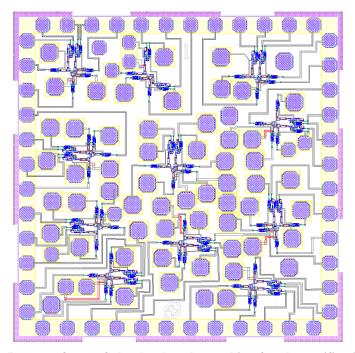

| Figure 4.17: A 1 | priliminary test chip designed for investigating the HYPRES Nb process   | 387  |

| Figure 4.18: Flo | oor planning for the JeSEF test chip                                     | 89   |

| Figure 4.19: De  | etails of the JeSEF test chip with locations of the various structures   | 90   |

| Figure 4.20: Flo | oor plan of the HYPRES test chip.                                        | 91   |

|                  |                                                                          |      |

|                  |                                                                          |      |

| Chapter 5        | Structural Testing: Defect Analysis of the RSFQ Processes                | ;    |

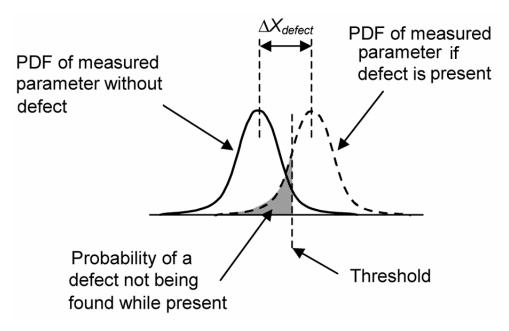

| Figure 5.1: Rea  | listic probability distribution function (PDF) of a measured parameter   | 99   |

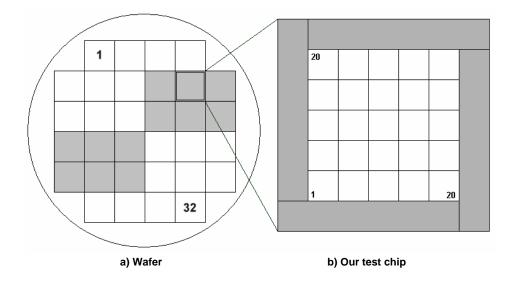

| -                | gram of a 6" SCE wafer showing the contours of test chips                |      |

| -                | tomicrograph of the test structure for detecting a crack in an M2 layer  |      |

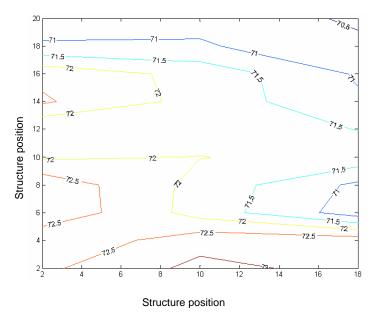

| Figure 5.4: Con  | tour plot showing parametric variation of the bias resistance            | 102  |

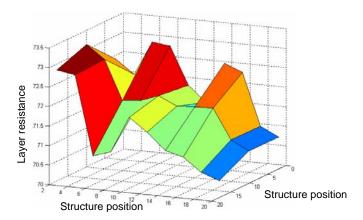

| Figure 5.5: Surf | face plot showing parametric variation of the bias resistance            | 102  |

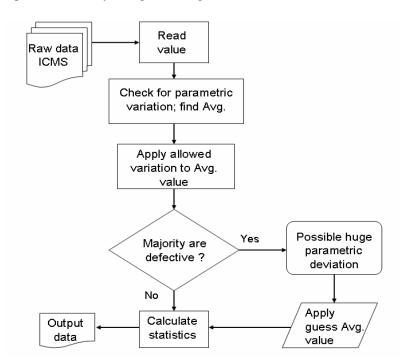

|                  | w chart of the implemented algorithm in MATLAB for defect analysis       |      |

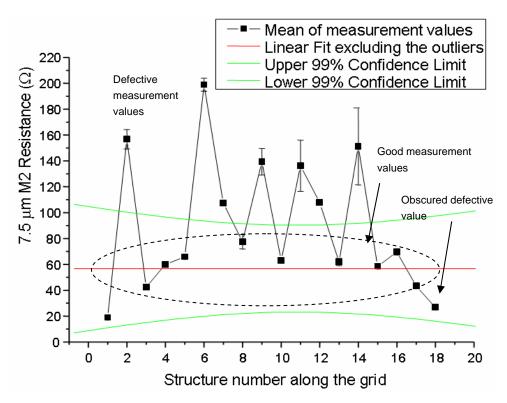

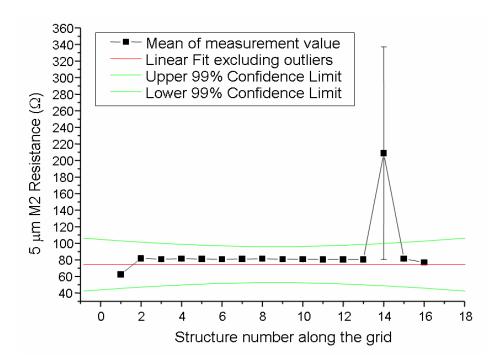

| Figure 5.7: Mea  | asurement results detecting step-coverage problems in the M2             | .104 |

| Figure 5.8: Mea  | asurement results showing the presence of a structural defect            | 105  |

| Figure 5.9: Res  | ults of the test structure for the bias resistor from JeSEF wafers       | 110  |

| Figure 5.10: Jes | SEF results for detecting step-coverage problems over a via              | .111 |

| Figure 5.11: Su  | mmary of results on the test structures for the JeSEF process            | .111 |

|                  | SEM photograph of a part of one of the realised JeSEF chips              |      |

| Figure 5.13: SE  | M photographs of the detected defects in the JeSEF process               | .113 |

| Figure 5.14: Ou  | Itline of the HYPRES test chip                                           | 114  |

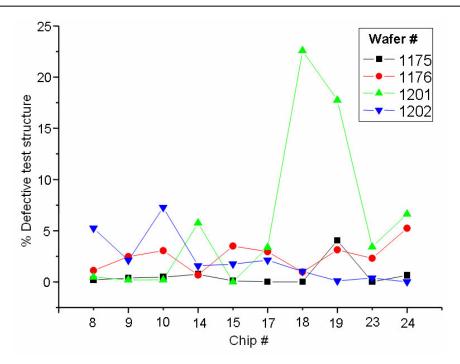

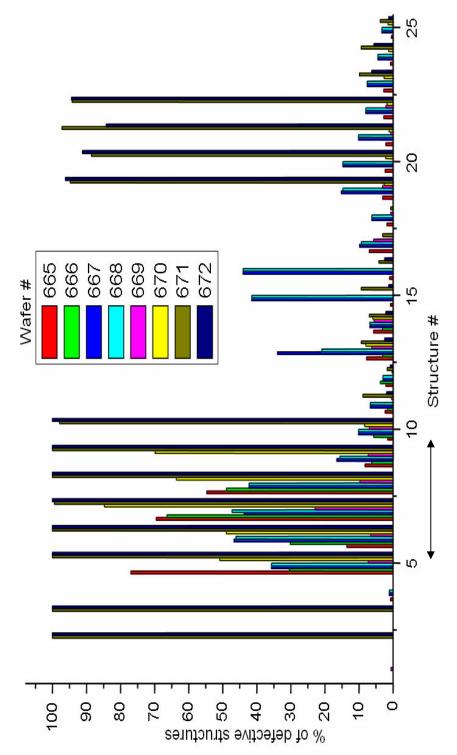

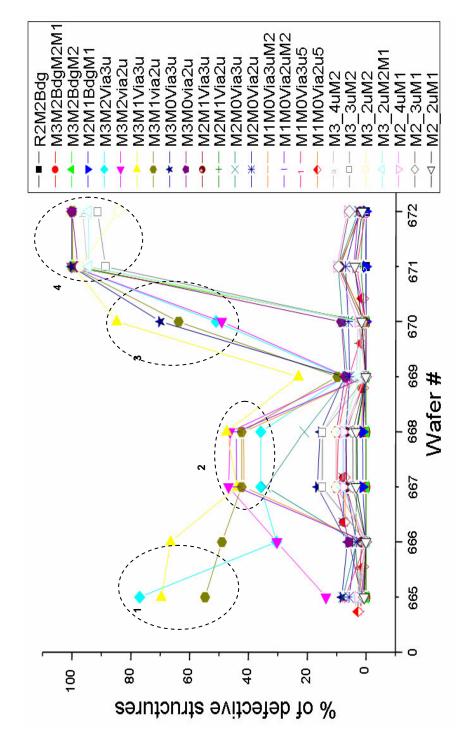

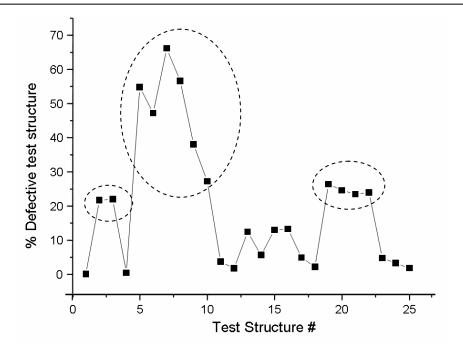

| Figure 5.15: Me  | easurement results on defective test structures for the HYPRES process.  | .120 |

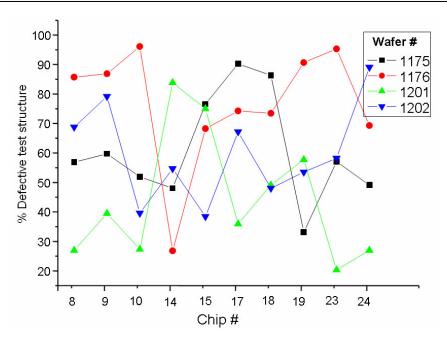

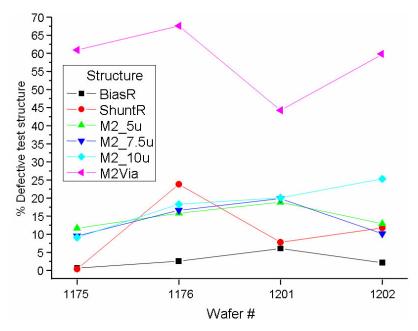

| Figure 5.16: Su  | mmary of results on the test structures for the HYPRES process           | .123 |

| Figure 5.17: Co  | omplete results on test structures for the HYPRES process                | .124 |

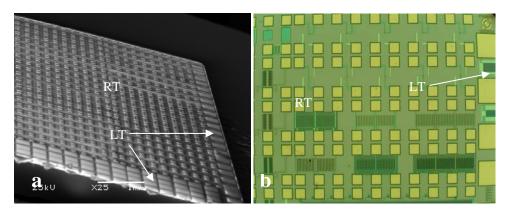

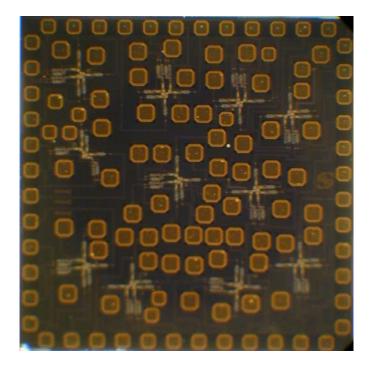

|                  | otograph of one of the realised HYPRES test chips.                       |      |

| Figure 5.19: SE  | M photographs of the detected defects in the HYPRES process              | .125 |

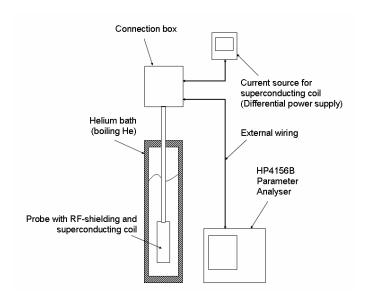

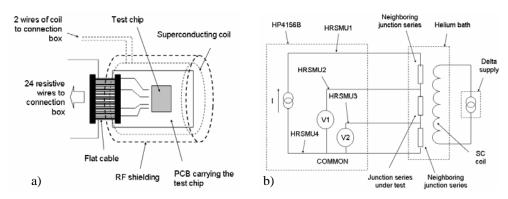

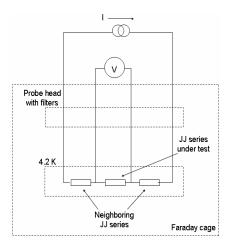

| Figure 5.20: Pro | oposed setup for I-V measurement                                         | .126 |

| Figure 5.21: Par | rts of the I-V measurement setup in detail.                              | .126 |

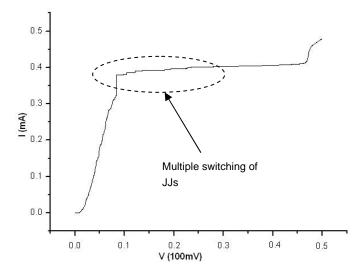

| Figure 5.22: An  | I-V plot from an HP4156B semiconductor parameter analyser                | .127 |

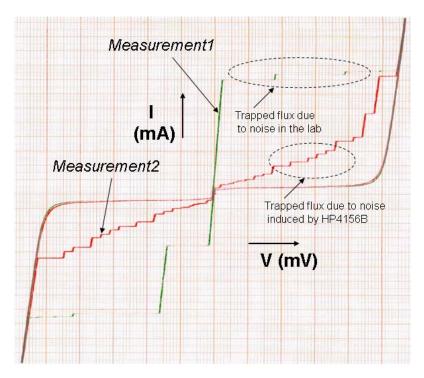

| Figure 5.23: Re  | peated I-V plot measurement with an analogue plotter for JJ series       | .128 |

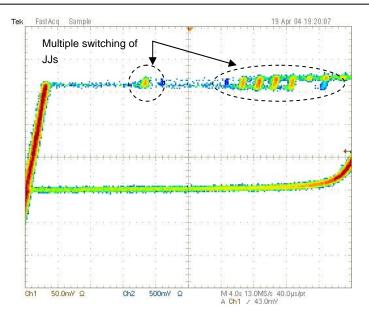

| Figure 5.24: An  | n enlarged portion of the I-V curve using a Tektronix scope              | .130 |

|                  | e modified experimental schematic for I-V measurements                   |      |

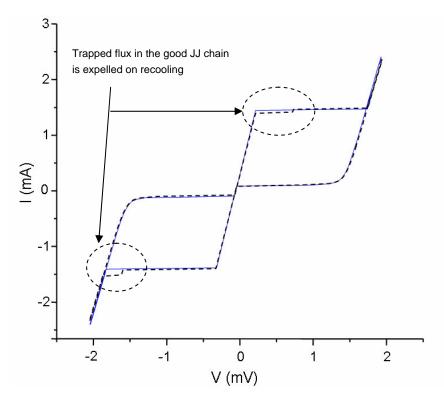

|                  | / plots of a series of good JJs                                          |      |

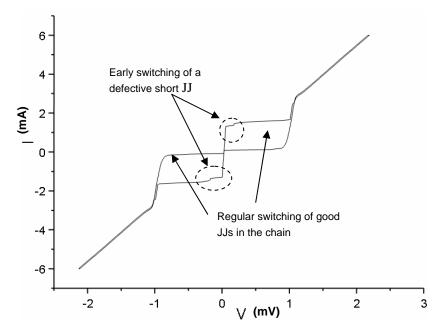

| -                | / plots of a series of JJs with a deliberately induced short defect      |      |

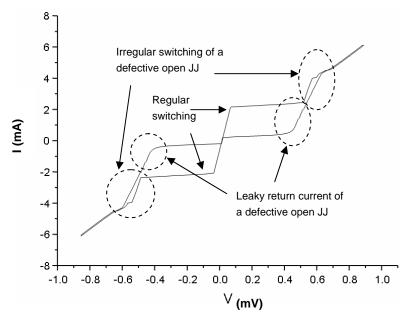

| Figure 5.28: I-V | I plots of a series of JJs with a deliberately induced open defect       | .134 |

List of Figures XV

#### Chapter 6 Defect-Based Testing of LTS RSFQ Circuits

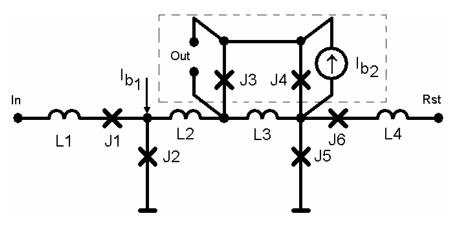

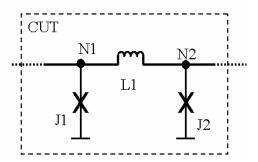

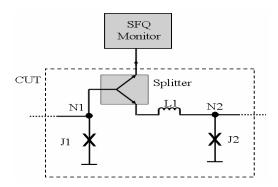

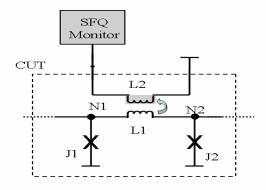

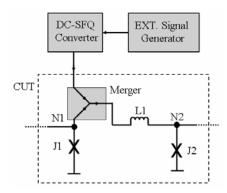

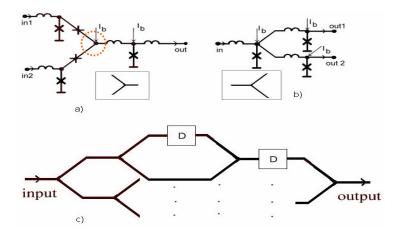

| Figure 6.1: Circuit schematic for a flux multiplier                                      | 139 |

|------------------------------------------------------------------------------------------|-----|

| Figure 6.2: Output of a simple flux multiplier.                                          | 140 |

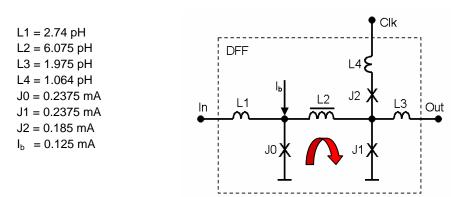

| Figure 6.3: Circuit scheme of an RSFQ D-type Flip-Flop                                   | 141 |

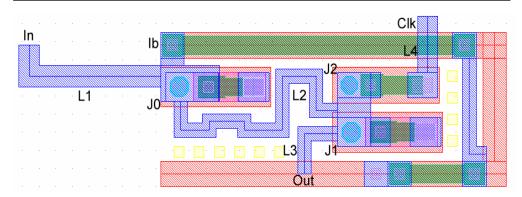

| Figure 6.4: Layout of a DFF in the JeSEF process                                         | 141 |

| Figure 6.5: Defect detection in a DFF using the I <sub>DDT</sub> testing technique       | 143 |

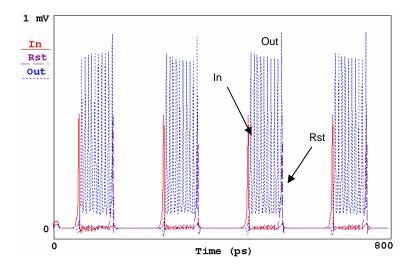

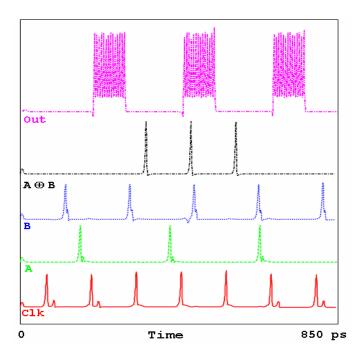

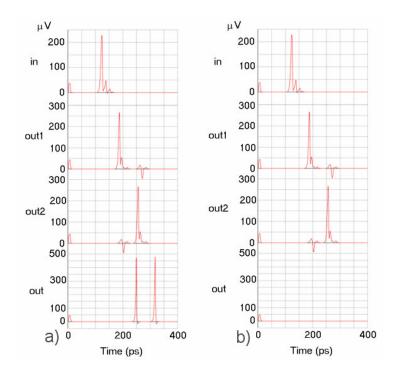

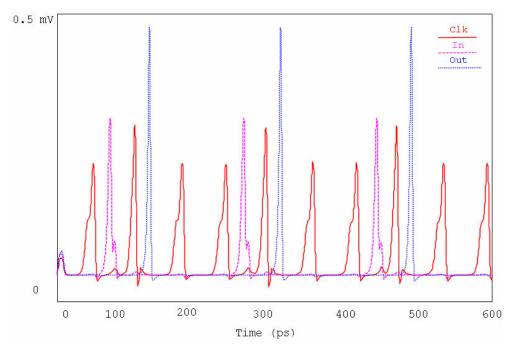

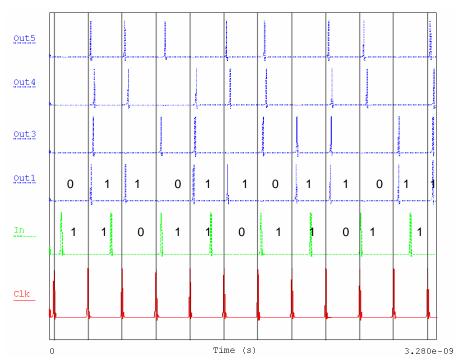

| Figure 6.6: Simulation of the fault-free operation of an RSFQ DFF                        | 144 |

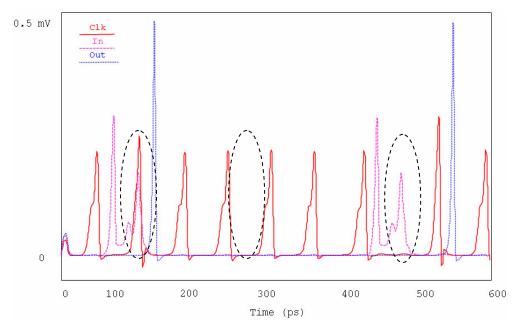

| Figure 6.7: Defect detection using digital structural testing: case a (input influenced) | 144 |

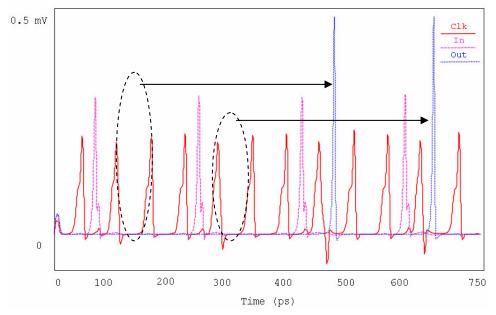

| Figure 6.8: Defect detection using digital structural testing: case b (delay)            | 145 |

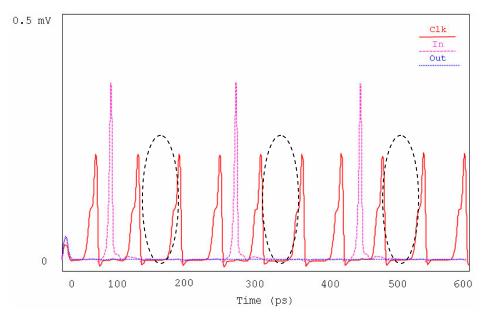

| Figure 6.9: Defect detection using digital structural testing: case c (no response)      | 146 |

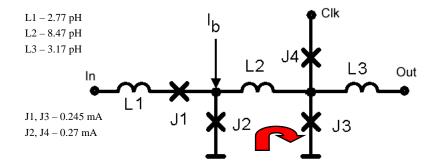

| Figure 6.10: Schematic of the RSFQ DFF designed in the HYPRES                            | 147 |

| Figure 6.11: Layout of an RSFQ DFF designed in the HYPRES Nb process                     | 148 |

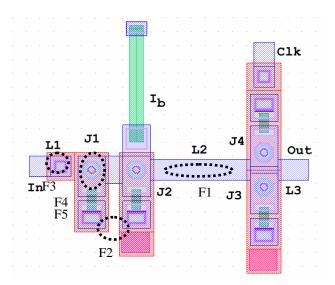

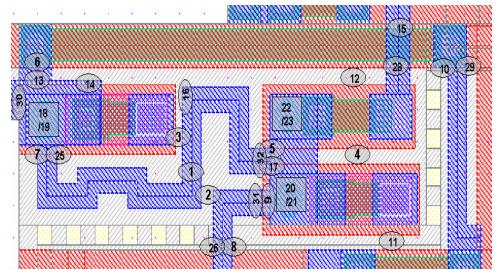

| Figure 6.12: Layout of a HYPRES DFF showing the defect-prone locations                   | 149 |

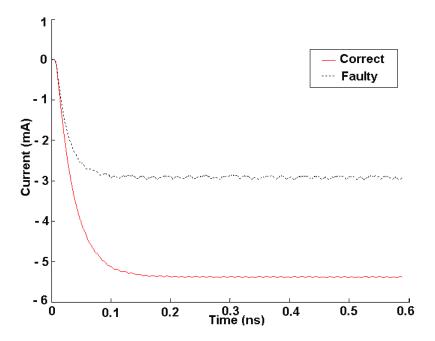

| Figure 6.13: Simulation experiments of an RSFQ DFF.                                      | 153 |

| Figure 6.14: Modified DFF schematic showing the formation of a new loop                  | 156 |

| Figure 6.15: DfT scheme for a general synchronous RSFQ logic gate                        | 157 |

| Figure 6.16: Schematic of the test circuit used for the verification of fault models     | 158 |

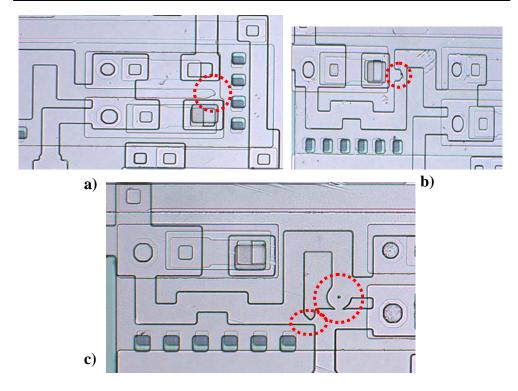

| Figure 6.17: Details of induced defects, parts of the DFF are shown                      | 159 |

| Figure 6.18: Cross-sections of induced defects.                                          | 160 |

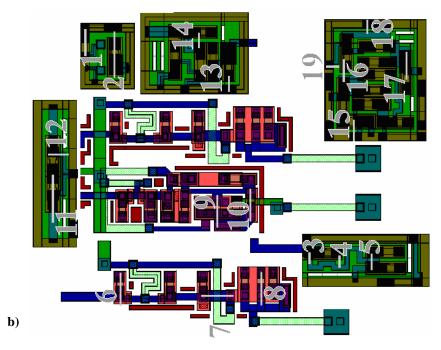

| Figure 6.19: Layout of the developed test-chips for the verification of fault-models     | 162 |

| Figure 6.20: Photograph of the developed test-chip for the verification of fault-models. | 162 |

| Figure 6.21: Photomicrographs of induced defects.                                        | 163 |

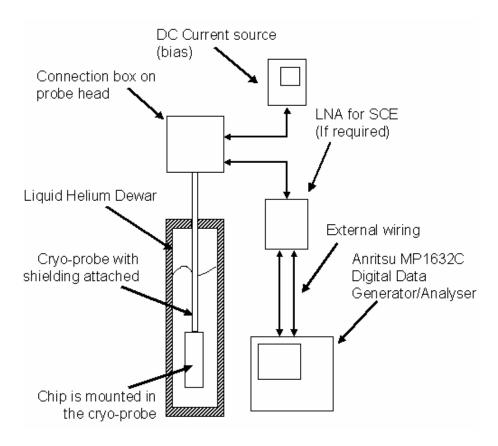

| Figure 6.22 Experimental set-up for the verification of fault models in SCE              | 164 |

# Chapter 1

## Introduction

Many of the semiconductor technologies are already facing limitations while new-generation data and telecommunication systems are implemented. Although in its infancy, superconductor electronics (SCE) is capable of handling some of these high-end tasks. Test methodologies for SCE are yet to be developed. A defect-based test methodology for SCE is presented in this thesis, so that systematic testing of complex systems can be implemented in this technology. In this chapter, the applicability of SCE is presented. The major issues to be tackled with regard to SCE and the outline of the thesis are also described in this chapter.

#### 1.1 Emerging High-Speed Applications

Requirements for efficient new-generation electronic systems in data and telecommunication industries are pushing the semiconductor technologies to their limits. Applications such as Software-Defined Radio (SDR) [1], petaflop computers [2] and high-speed network routers [3] are extremely difficult to implement and are very complex in nature. As the RF and digital domains converge, entirely new strategies are needed to enable the innovative applications that will drive tomorrow's electronics industry.

The wireless communications industry with its unquenchable thirst for bandwidth in digital telecommunications requires future data converters and digital signal processors to deliver greatly increased performance to meet the connectivity demands of users. Due to the rapid increase of mobile communication systems, the available RF spectrum gets more and more crowded. Hence an efficient frequency allocation and usage is necessary to meet the demands of industry. SDR for Base Station (BS) applications, where analog-to-digital conversion is one of the enabling technologies, as explained in [1], is a promising concept for the wireless communication industry since the entire transceiver function can be implemented in software, avoiding the replacement of hardware each time the system has to be upgraded.

However, the practical implementation of such a system is dependent on the hardware, which consists of precise, ultra high-speed electronic devices such as Analogue-to-Digital Converters (ADCs). The present and near future semiconductor ADCs cannot be used for the implementation of SDR BS in the near future [4]. Some of the factors that hamper the implementation are the requirements of very high speed at a few tens of GHz and the high resolution (e.g. 16 bits) at these speeds and bandwidth.

The hyper-computer business demand for access to intensive computation for weather prediction, non-invasive geo-physical exploration of natural resources, global economic modelling, intensive data mining, and other applications already exceeds the abilities of modern supercomputers and networks. Ever-faster processing capabilities, ultra-low latency memories, and ultra-high throughput network switches will be required in the future.

Currently, high-performance CMOS-based microprocessors have reached a clock frequency of about 4 GHz, and a microprocessor assembly featuring about 125 million transistors are placed on a single 112 mm<sup>2</sup> chip [5]. The heat dissipation in the worst case situation can be up to about 115 watts (similar microprocessor for mobile applications can dissipate up to 88 W at 3.5 GHz while those for embedded applications up to 27 W at 2 GHz) [6]. The peak performance of such a CMOS multiprocessor chip can be crudely estimated as 10 to 100 gigaflops based on a very optimistic assumption of the fabrication technology [7].

To achieve a peak performance of 1 petaflops will take 10 to 100 thousand advanced CMOS chips discussed above, with total power consumption in the order of 10 MW. The management of power of such proportions would take a sizeable building. The significant (microsecond-scale) latency of interprocessor communication in a system of such a

Figure 1.1: Microphotograph of the Flux-1 RSFQ microprocessor (Courtesy: NGST).

physical size would make the system stall for programs where inter-processor communication is a significant fraction of the computational process. More recent semiconductor technologies like the complementary GaAs technology are also far behind in performance for these requirements [8]. Alternatives like grid computing using distributed computing principles are being tried extensively to solve the need for high-performance systems [9].

Furthermore, the defense/government market with a never-ending drive to do more with less is resulting in a concentrated push to deploy multifunction, dynamically reconfigurable systems. Such systems will rely on flexible, ultra-fast, digital technologies, and replace, consolidate, and expand the capability of existing dedicated analogue systems for radar, electronic warfare, and other surveillance applications.

#### 1.2 Super-Conductor Electronics (SCE)

In the near future, current semiconductor technologies will not always be able to provide efficient solutions for the speed, accuracy and power requirements for the applications mentioned in the previous section. SCE is an emerging technology in which the active element, a Josephson Junction (JJ), work in the superconducting state of the materials used for its fabrication. The operating temperatures of these systems are much below room temperature. According to the International Technology Roadmap for Semiconductors (ITRS) 2005, SCE will address several important specific applications that are beyond the scope of semiconductors [10]. A detailed discussion about SCE is presented in chapter 2 of this thesis.

A number of commercial enterprises have started developing systems in SCE. IBM was one of the first to start research in SCE. But the activities were stopped due to problems in the pre-mature technology for realizing these SCE circuits. Later, after the invention of Rapid Single-Flux Quantum (RSFQ) logic [11], and the development of the planar tri-layer process [12], the limitations in realizing medium-complex SCE circuits were eliminated. In

the past few years, extensive research has been carried out with regard to the development of high-end complex systems in SCE. Examples of these complex designs are a superconductor ADC [13] targeted towards SDR BS developed by MIT in collaboration with IBM which was fabricated by HYPRES Inc. NY, the Flux microprocessor chip [14] for the US defense petaflops program by TRW Space and Electronics (now Northrop Grumman, CA) as shown in Figure 1.1 and a GHz packet switch [15] by NEC, Japan for high-speed networks.

RSFQ logic is a new family in SCE for future Integrated Circuit (IC) technology with the potential to leapfrog the performance of traditional silicon and III-V compound semiconductors. ICs with sub-micron RSFQ static digital frequency dividers and Toggle flip-flops have already been fabricated and operated in university laboratories at over 750 Gb/s [16], [17]. These achievements represent faster demonstrated electronic circuit speeds than any other technology has predicted today, even via computer simulations.

The RSFQ technology also has a clear path to extend performance. Unlike semiconductor devices, the speed of RSFQ ICs comes from inherent physical phenomena, not advanced scaling. This means that existing lithography techniques can be employed, and more importantly, existing equipment can fabricate circuitry that surpasses conventional limits of performance. Because RSFQ logic uses the lossless ballistic transmission of digital data as "fluxons" or a magnetic-flux quantum near the speed of light, the wire-up nightmare that silicon designers face is substantially reduced. This scenario also allows the full speed potential of individual gates to be realized.

The speed and power problems associated with semiconductor processors have stimulated a search for alternative approaches to petaflops-scale computing. Preliminary design work shows that an RSFQ microprocessor using a much more conservative, 0.3 µm fabrication technology can house just about 30 million JJs (active elements) on a chip of comparable area. Operating at a clock frequency of about 90 GHz it would be able to provide a peak performance of approximately 2,000 gigaflops, while the dissipating power would be below the 1 Watt level. The Hybrid Technology MultiThreaded architecture (HTMT) project based on the use of RSFQ technology with its "COOL" core [7] indicates that the 1-petaflops peak performance might be reached with just 500 logic chips (plus about 2,000 fast superconductor memory chips), with aggregate power dissipation in the core below 1 kW. Although the removal of such power from the cryostat (the container in which the RSFQ IC chips are kept at their cold superconducting temperature) would require a large-scale close-cycle cryocooler (helium recondenser) consuming about 300 kW, this is still considerably less than what would be required for a CMOS-based system. Even more important, the cryocooler would be remotely placed, enabling to compact the RSFQ core into a 1 m<sup>3</sup> volume. As a result, the simulated average latency of the interprocessor communication network (including both switching delays and signal time-offlight) is as low as 20 ns, apparently enabling the system as a whole to sustain a subpetaflops performance in many real-life computer programs [18].

Other features of this technology that make it suitable for growth into the traditional market include its compatibility with existing IC packaging techniques. These include

compatibility with optical (fiber) signal input and output, a maturing multi-chip module (MCM) technology with multi-Gb/s digital data transfer between chips, and simple interface circuits to convert to and from both ECL logic and CMOS logic levels [19], [20].

Even at this immature stage, SCE is capable of handling these tasks. Having a very high theoretical speed limit with the accuracy of a magnetic-flux quantum and very-low power consumption, SCE is a promising candidate for the high-end future applications. The most important hallmarks of SCE are summarized as:

- extremely non-linear current–voltage (I–V) and resistance–temperature (R–T) characteristics of the active elements, the JJs;

- high frequency of operation;

- high resolution and speed;

- magnetic-flux quantum limited sensitivity;

- low dissipation, dispersion, noise and loss;

On the other hand, there are reasons and situations, which may decrease the motivation for using SCE:

- cooling and cryogenics add additional costs, power requirements, weight and possible vibrations to the system;

- its sensitivity could in some cases mean saturation from other incoming signals or from electromagnetic interference (EMI) and hence special care has to be taken;

- if price versus performance gives no advantage (for e.g. small scale applications);

- if other technologies solve the problem more efficiently (for e.g. usage of SCE in a personal computer).

Main disadvantage of an SCE system is the requirement of cooling the device to superconducting temperatures. But the high-end applications such as SDR and petaflops computer require cooling even if semiconductor technologies are used and intense research is carried out to bring the SCE systems like an ADC to "high" temperatures by developing them in high-temperature superconductor (HTS) technology as opposed to low-temperature superconductor (LTS) technology. SCE finds its application when ultra-high speed switching or processing of large volume of data per unit time is required.

#### 1.3 Problem Definition and Chosen Approach

Since RSFQ circuits work at extremely high speeds, testing and verification of such a device is a difficult and challenging task. Direct testing at these speeds is not possible at this moment. Furthermore, the costs of the equipment required for such tests would be extremely high. Hence methods have to be developed to reduce the requirements of external hardware for the test. In systems consisting of several thousands of gates, the trend

is to introduce certain testability options at the design phase. Main goal of this Design for Testability (DfT) approach is to enable structural testing and Automatic Test Pattern Generation (ATPG) by insertion of additional logic. This is desirable, as the system under study is complex; hence it is not possible to test all components directly within the system. A DfT-based approach is essential for commercial production of complex systems in SCE.

As the complexity of the SCE circuits has increased beyond 63,000 JJs per chip as in the case of a Flux microprocessor chip [14], realization of a working design becomes an extremely difficult task. Although extended research is going on in making complex circuits and scaling down the minimum sizes, very little or no information is available in the literature on the methodology for defect analysis for superconductor electronics. The yield levels are much lower in SCE than in the semiconductor industry. One of the reasons is due to the fact that little information is available on superconductor process defects and hence little improvement can be made.

In semiconductor microelectronics, special test structures have been developed and realized along with the functional integrated circuits. The information gathered using these test structures are used for yield analysis and improvement and defect-oriented testing. As mentioned before, little information is available on probable defects in SCE process and test methodologies. More detailed information supporting this issue can be found in the special issue on applications of superconductivity of the Proceedings of the IEEE [21].

Development of a measurement methodology for defect analysis in SCE was one of the problems that have been tackled during our research. Major issues handled during this process were ease of measurement and measurement time for quick determination of the existence of defects. For this purpose, two RSFQ processes were investigated and subsequent results are presented in this thesis [22]. Special test structures were developed and realized along with the ICs for the RSFQ process. The measurement methodology and results on structures that have been developed to detect the top-ranking defects that can occur in a Niobium tri-layer based technology are presented [23].

The information gathered using these test structures are primarily used for DBT. Based on this information, a DBT has also been conducted and those results are presented leading to possible test methodologies for RSFQ circuits. From the data, potential defect-prone areas can be detected within the circuit and DfT structures can be introduced to monitor the status while employing the DBT approach. In this thesis, the possibilities of DfT for SCE circuits in view of the DBT approach are also presented.

Fault models have been developed after studying the behaviour of the test structures. These fault models are subsequently used for fault simulation of the circuit for development of an ATPG technique. The ultimate goal is to develop ATPG for SCE logic circuits. Investigating the possibility of whether or not the available ATPG techniques are applicable is one of the major concerns in the process. Otherwise new ATPG techniques have to be specifically developed for SCE. Information about defects and their subsequent translation into fault-models are crucial at this stage as little is known about the defects that

can occur in an SCE fabrication process [21], and especially under superconducting circumstances.

As part of DBT, various fault models have been proposed for SCE circuits. These are theoretical models based on work in structural testing and analysis of SCE processes. Until now, such models have not yet been verified. As the ultimate goal is to develop ATPG for SCE circuits to guarantee a high quality, verified fault models are required before going ahead with ATPG approaches. A test methodology based on a DfT approach is required for the physical verification of the abstracted fault models. The fact that an individual Single Flux Quantum (SFQ) pulse is extremely difficult to be detected was hampering the verification process. DfT schemes have been proposed to detect an individual SFQ pulse [24]. This technique is applied to a simple RSFQ logic circuit to verify the proposed fault models.

As a continuation of the research in DBT of an RSFQ D-type Flip-Flop (DFF), extensive studies were conducted on such a DFF realised in a mature Nb process at HYPRES Inc., NY. HYPRES is one of the leading SCE foundries where commercial production of RSFQ devices has been started. The defect-prone locations in the DFF were identified and defects were deliberately inserted into the device. Simulation experiments showed that ATPG could be possible with adaptation/modification of the techniques for SCE, but needs verification by means of extensive experiments. Ultimately, the development of SCE systems including DfT hardware is required if they are to be used in commercial applications [25]. In our investigation, Built-In-Self-Test (BIST) feasibility study was carried out for an SCE Delta ADC being developed for SDR application. But the focus changed to defect detection and fault models as the relevant metrics were not available to proceed with BIST [26].

#### 1.4 Outline of the Thesis

In this section, the outline structure of the thesis will be discussed.

Chapter 2 introduces the reader to the RSFQ logic family of circuits. The chapter starts with an introduction to SCE. A JJ is described along with circuit models and associated SCE circuits in the RSFQ logic family are presented in detail. The design and implementation of RSFQ circuit with an example of a DFF is also elaborated. Advantages and disadvantages of using RSFQ circuits based on the latest developments are in addition mentioned in this chapter.

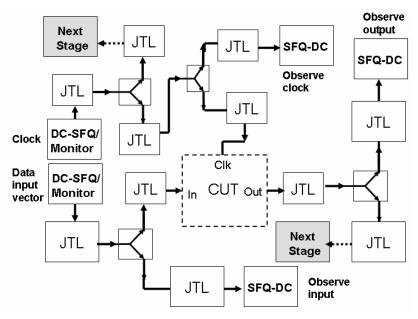

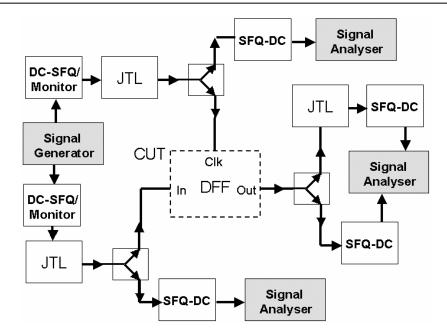

Chapter 3 starts with an introduction to IC testing. Functional, structural and DBT is elaborated followed by the selection of defect-monitor test structures for fabrication process analysis. Various types of structures are mentioned and the measurement techniques used for them is explained. DfT is discussed with possible structures for the defect-based testing of RSFQ circuits. It is demonstrated how SFQ pulses can be monitored at an internal node of an SCE circuit by Test Point Insertion (TPI). The available features in the proposed design for customising the detector make it attractive for a detailed DBT of

RSFQ circuits. The introduction of a test signal in an RSFQ circuit using TPI is also being illustrated.

Chapter 4 starts with a short introduction of superconductor processes used for RSFQ circuit realisation. Different types of processes are mentioned to get a general idea about them. Finally, the two LTS RSFQ processes which were investigated during this research work are presented in detail. A structural measurement methodology has been applied to both processes, leading to the detection of various probable defects that can occur in them. Defect-monitor test structures were developed as part of the research so as to determine the defect statistics in these processes. The applied test methodology as well as the structures are presented in detail for both processes. This chapter concludes with the design implementation of test chips incorporating the above mentioned test structures. The classification of defects in an RSFQ process is also presented.

Chapter 5 deals with the experimental analysis of the test chips developed for the structural testing of RSFQ processes. The two processes described in the previous chapter which were investigated during this research work are analysed. Methodologies for the measurements are also presented. Implementation of the test-routines for semi-automatic testing of the processed chips for structural defects at room temperature has been carried out. The test data is analysed to provide defect statistics of both processes. This chapter presents the defect ranking of the processes leading to the most probable defects in a process. Measurement methodologies for low temperature (LT) measurements are also presented and it is proven that the approach is able to detect the defects in a JJ. A DBT approach is presented for fabrication-process analysis. The presented defect-monitor structures are used to gather statistical information, i.e. the probability of the occurrence of defects in the process. This forms the first step for Inductive Fault Analysis (IFA), a commonly used DBT methodology.

Chapter 6 deals with the methodologies applied for the testing of RSFQ circuits. Modelling and the influence of a defect that can create an error in an RSFQ circuit are subsequently described using circuit simulations in Chapter 6 of this thesis. Development of fault models for RSFQ circuit testing is covered in this chapter based on the results from the developed defect-monitoring test-structures. Two types of DBT methodology are enumerated in this chapter. The preliminary investigation leads to a detailed study on an RSFQ DFF. Test chips have been developed incorporating defect-induced DFFs to study the actual behavior when the probable defects are present in the realized circuit. This chapter concludes with the design implementation of test chips which will be used for the verification of the developed fault models in the future.

Finally, Chapter 7 gives a summary of the obtained results. The conclusions are discussed with future research possibilities into ATPG and yield analysis of RSFQ-based systems.

#### 1.5 References

- [1] J. Mitola, "Software radio architecture evolution: foundations technology tradeoffs, and architecture implications", IEICE Trans. Commun., Vol. E83-B, June 2000, pp. 1165–1173.

- [2] Y. Oyanagi, "Future of supercomputing", J. Comp. Appl. Math., Vol. 149/1, December 2002, pp. 147-153.

- [3] B. Sultan, "A switch-router taxonomy", Comp. Commun., Vol. 21/2, March 1998, pp. 101-110.

- [4] R.H. Walden, "Analog-to-digital converter survey and analysis", IEEE JSAC, Vol. 17, April 1999, pp. 539-550.

- [5] D. Boggs, A. Baktha, J. Hawkins, D. T. Marr, J. A. Miller, P. Roussel, R. Singhal, B. Toll, K. S. Venkatraman, "The Microarchitecture of the Intel Pentium 4 Processor on 90 nm Technology", Intel Tech. Jour., Vol. 8, Feb 2004, pp. 1-17.

- [6] Thermal Design Power (TDP) of Intel Pentium 4 processors, Intel data sheets http://www.intel.com/design/pentium4/documentation.htm.

- [7] M. Dorojevets, P. Bunyk, D. Zinoviev, and K. Likharev, "COOL-0: Design of an RSFQ subsystem for petaflops computing", IEEE Trans. Appl. Supercond., Vol. 9, June 1999, pp. 3606-3614.

- [8] R. Brown, B. Bernhardt, M. LaMacchia, J. Abrokwah, P. N. Parakh, T. D. Basso, S. M. Gold, S. Stetson, C. R. Gauthier, D. Foster, B. Crawforth, T. McQuire, K. Sakallah, R. J. Lomax and T. N. Mudge, "Overview of Complementary GaAs Technology for High-Speed VLSI Circuits", IEEE Trans. VLSI Circ., Vol. 6, March 1998, pp. 47-51.

- [9] For a detailed study see Grid Computing: Special Issue of IBM Systems Journal, Vol. 43, October 2004.

- [10] In section: Emerging Research Devices, the International Technology Roadmap for Semiconductors (ITRS) 2005 – http://www.itrs.net/Common/2005ITRS/ERD2005.pdf.

- [11] K. Likharev, "Rapid single flux quantum (RSFQ) logic", Encyclopaedia of Materials, Science and Technology, Elsevier, 2002, an electronic version of the document is available at: <a href="http://www.elsevier.com/mrwclus/15/183/35/index.htt">http://www.elsevier.com/mrwclus/15/183/35/index.htt</a>.

- [12] M. Radparvar, M. Berry, R. Drake, S. Faris, S. Whiteley and L. Yu, "Fabrication and performance of all NbN Josephson junction circuits", IEEE Trans. Magnet., Vol. 23, March 1987, pp. 1476 –1479.

- [13] J. F. Bulzacchelli, L. Hae-Seung, J. A. Misewich and M. B. Ketchen, "Experimental Demonstration of Superconducting Bandpass Delta-Sigma Modulator", IEEE Trans. Appl. Supercond., Vol. 13, June 2003, pp. 471-476.

- [14] M. Dorojevets and P. Bunyk, "Architectural and Implementation Challenges in Designing High-Performance RSFQ Processors: A FLUX-1 Microprocessor and Beyond", IEEE Trans. Appl. Supercond., Vol. 13, June 2003, pp. 446-449.

- [15] S. Yorozu, Y. Kameda, Y. Hashimoto and S. Tahara, "Single Flux Quantum Packet Switch Circuits for Large-scale Communication Systems", IEEE Trans. Appl. Supercond., Vol.13, June 2003, pp. 450 453.

- [16] W. Chen, A. V. Rylyakov, V. Patel, J. E. Lukens and K. K. Likharev, "Superconductor digital frequency divider operating up to 750 GHz," Appl. Phys. Lett., Vol. 73, November 1998, pp. 2817-2819.

- [17] W. Chen, A. V. Rylyakov, V. Patel, J. E. Lukens and K. K. Likharev, "Rapid single flux quantum T-flip flop operating up to 770 GHz," IEEE Trans. Appl. Supercond., Vol. 9, June 1999, pp. 3212-3215.

- [18] K. Likharev, "Superconductor Devices for Ultrafast Computing", in H. Weinstock, ed., "Applications of Superconductivity", Kluwer Academic Publishers, Dordrecht, 1999, ISBN: 079236113X.

- [19] Q. P. Herr, M. S. Wire and A. D. Smith, "Ballistic SFQ signal propagation on-chip and chip-to-chip", IEEE Trans. Appl. Supercond., Vol. 13, June 2003, pp. 463-466.

- [20] N. Harada, A. Yoshida and N. Yokoyama, "High-speed demonstration of an output interface driver for single-flux quantum systems", IEEE Trans. Appl. Supercond., Vol. 12, September 2002, pp. 1852-1856.

- [21] L. Abelson and G. L. Kerber, "Superconductor Integrated Circuit Fabrication Technology", Proc. IEEE, Vol. 92, October 2004, pp. 1517 1533.

- [22] A. A. Joseph and H.G. Kerkhoff, "Towards Structural Testing of Superconductor Electronics", Proc. IEEE International Test Conference (ITC) 2003, pp. 1182-1191.

- [23] A. A. Joseph, S. Heuvelmans, G. Gerritsma and H. G. Kerkhoff, "Test Structures and their Application in Structural Testing of Digital RSFQ Circuits", Physica C, Vol. 403, March 2004, pp. 103-111.

- [24] A.A. Joseph and H.G. Kerkhoff, "Design for the Testability of Superconductor Electronics" Superconductor Science and Technology, Vol. 16, December 2003, pp. 1559-1565.

- [25] A. A. Joseph, M. H. H. Weusthof and H. G. Kerkhoff, "Application of DfT techniques to a 20 GHz superconductor delta ADC", Micro. Elec. Jour., Vol. 33, October 2002, pp. 791-798.

- [26] H. G. Kerkhoff, A. A. Joseph, S. Heuvelmans, "Testable Design and Testing of High-Speed Superconductor Microelectronics" Proc. IEEE International Workshop on Electronic Design, Test and Applications (DELTA) 2002, pp. 8-12.

# Chapter 2

# Superconductor Electronics for Digital Applications

This chapter introduces the Rapid Single Flux Quantum (RSFQ) logic family of circuits. It starts with an introduction to Super-Conductor Electronics (SCE). A Josephson junction (active element) is described along with circuit models and associated SCE circuits and the RSFQ logic family is presented in detail. The design and implementation of RSFQ circuits with as example a D-type flip-flop is also discussed. Advantages and disadvantages of using RSFQ circuits and the latest developments are also mentioned in this chapter.

#### 2.1 Introduction

As mentioned in the previous chapter, Superconductor Electronics (SCE) is emerging as one of the technologies for future high-end applications. Various schemes were proposed for implementing logic circuits in SCE. Now-a-days, the most widely used SCE logic is Rapid Single Flux Quantum (RSFQ) logic and the essential elements are Josephson Junctions (JJ), inductors and resistors for biasing and shunting the junctions. A JJ, the basic active element of an SCE circuit, is formed if two superconductors are separated by an interface of nanometre dimensions. The operation of a JJ is based on the quantum mechanical tunnelling across this dielectric barrier interface [1]. Inductors are of two types, storage and normal (non-storage). Storage inductances have relatively higher values than normal ones, so that the loop containing a JJ will be able to store a magnetic flux quantum or a fluxon [2]. RSFQ circuits use very little power because they remain in superconducting state except while switching of a JJ during its operation, which lasts only for a few pico-seconds. In practice, a negative bias voltage, resulting in a negative bias current, is applied to the RSFQ circuit for the correct operation.

The Josephson Effect was predicted by Brian Josephson in 1962 while he was a student at Cambridge University [3]. The first Josephson devices were made by Philip Anderson and John M. Rowell at Bell Laboratories in 1963 [4]. In a modern Josephson device, the operation is resulting from the tunnelling of electrons pairs through its thin barrier. These pairs of electrons, called Cooper pairs, carry current in superconductors [5]. The insulating barriers are called weak links because the Cooper current through them is only a small fraction (~ 1/1000) of the maximum pair current that can be carried in the superconductor electrodes. Tunnelling through the gate oxide is undesirable in silicon field effect transistors, while in Josephson junctions the tunnelling current is essential. From the mid-'60s to the mid-'80s, superconductor digital ICs relied on logic schemes in which Josephson junctions with hysteretic I-V curves were switched from the superconducting (0) state to the resistive (1) state. In today's RSFQ technology, the junctions are shunted externally with a resistor, so the I-V characteristic becomes nonhysteretic. This allows circuit designers to exploit another superconductivity phenomenon: the macroscopic quantization of magnetic flux [1]. In RSFQ circuits, it is not a static voltage level, but the presence or absence of quantized magnetic flux or fluxons that represent information bits [6], [7].

The organisation of the chapter will now be outlined. Section 2.2 deals with a JJ and associated models. JJ circuits are described in Section 2.3. Design and implementation of RSFQ circuits are presented in Section 2.4. Advantages and disadvantages of RSFQ circuits are described in Section 2.5.

#### 2.2 Josephson Junctions

The fact that a superconductor can exist in two states: the resistive (normal) state and the superconducting state, is used for practical applications involving switching. One of the first devices to be used in logic operations was a cryotron [8] proposed by Dudley Buck of

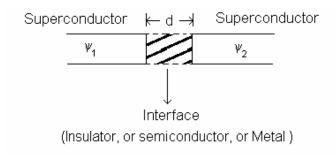

Figure 2.1: Schematic of a Josephson junction.

MIT Lincoln Labs in 1956 and was the first practical application of superconductivity. It consisted of a short gate wire of a low critical-field superconductor surrounded by a solenoid coil of a high critical-field superconductor. A sufficient solenoid current  $I_c$  can cause the field at the surface of the gate wire to exceed the critical current, therefore causing the gate wire to exceed the critical field and causing the gate to become resistive. If  $I_c$  is then reduced, the gate again becomes superconductive. Several circuits were suggested using a cryotron, a detailed discussion can be found in [9]. The major problems faced were reproducibility and yield. The basic devices were predicted to have an operating frequency of up to a few hundred MHz. Another factor which had to be taken care of was avoidance of high-inductance loops as well as a high relative power consumption.

As mentioned before, the discovery of the Josephson Effect made a difference in SCE. A JJ is formed if two superconductors are separated by an interface which can be an insulator, metal or semiconductor with a thickness of a few nanometres. Figure 2.1 shows a schematic of a JJ. If  $\psi_1$  and  $\psi_2$  are the macroscopic wave functions describing the superconductors with a phase difference of  $\varphi$ , a supercurrent will flow through the JJ [1]. This supercurrent is not a function of voltage, but of the phase difference of the wave function between the electrodes and is given by the equation:

$$I_{s} = I_{c} \cdot \sin \phi \tag{2.1}$$

where  $I_c$  is the critical current being the maximum supercurrent that the junction can handle. This is called the DC Josephson effect: a supercurrent can flow through a JJ, without a voltage being present across the junction. This holds for supercurrents smaller than the critical current of the junction. The presented situation is referred to as the superconducting or stationary or S-state of the junction. If a voltage V is applied across the JJ, the phase difference ( $\phi = |\psi_1 - \psi_2|$ ) will vary and the current across the JJ will oscillate with frequency:

$$\omega = \frac{2e}{\hbar} \cdot V \tag{2.2}$$

and amplitude  $I_c$ , where e is the elementary charge ( $e \approx 1.60 \cdot 10^{-19}$  C) and  $\hbar$  is given by:

$$\hbar = \frac{h}{2\pi} \tag{2.3}$$

where h is the Planck's constant (h  $\approx 6.63 \cdot 10^{-34}$  Js). This is called the AC Josephson effect and given by the equation [10]:

$$\omega = \frac{d\phi}{dt} = \frac{2e}{\hbar} \cdot V = \frac{2\pi}{\Phi_0} \cdot V \tag{2.4}$$

where  $\Phi_0$  is the magnetic flux quantum;  $(\Phi_0 \approx 2.07 \cdot 10^{-15} \text{ Vs})$ .

If a non-zero voltage is present across the junction at a non-zero (0 Kelvin) temperature T, there will be an oscillating supercurrent  $I_S$  as well as a normal current  $I_N$  present. The normal current is due to thermal motion of the charge carriers; some Cooper pairs will be broken, after which one of the carriers will tunnel across the barrier. This current becomes dominant in the situation where the energy supplied by the voltage across the junction is greater than the binding energy of a Cooper pair (2 $\Delta$ ). The described situation occurs as the junction voltage approaches the gap-voltage,  $V_g$ :

$$V_g = \frac{2\Delta(T)}{\rho}.$$

(2.5)

For situations where  $|V| > V_g$ , the  $I_N$ -V relation can be approximated by the usual Ohmic dependence:

$$I_N = G_N V = \frac{V}{R_N} \tag{2.6}$$

where  $I_N$  is the normal current through the junction, V is the voltage over the junction,  $G_N$  is the junction's normal-state conductance and  $R_N$  the normal-state resistance. A JJ remains in its superconducting state only if the supercurrent  $|I_S|$  is smaller than the critical current of the junction. Any additional current through the junction will be carried by  $I_N$ , which will result in a non-zero voltage across the junction. Therefore, when the junction current exceeds its critical current, the junction will go into the resistive or R-state.

Junctions are often characterized by their  $V_C$  parameter or "the  $I_CR_N$  product". In the R-state, the supercurrent  $I_S$  oscillates with a mean value zero. When considering the I-V curve of a JJ, the oscillating supercurrent does not contribute to the DC current value. For  $|V| > V_g$  the I-V relation of the junction is approximately given by equation (2.5). In case  $|V| < V_g$  the mechanism responsible for the normal (tunnelling) current will not contribute. In this voltage range the DC current will consist only of the supercurrent, which has a zero mean value. A more detailed treatment on JJs can be found in [1], [10].

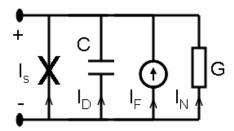

Figure 2.2: Circuit model of a Josephson junction.

#### 2.2.1 Junction Models

One of the most widely used simulation models for a JJ is the RSJ model [11], [12] as shown in Figure 2.2. The Resistively Shunted Junction or RSJ model uses simple relationships to express the current components of a JJ. For the supercurrent it uses (2.1) and (2.4), for the normal current it uses equation (2.6). In this model two more currents occur in the junction apart from the supercurrent  $I_S$  (denoted by "X" in the model) and the normal current  $I_N$  being a fluctuation current and displacement current. The fluctuation current ( $I_F$ ) is a noise current, which can for example be modelled as thermal noise. The displacement current ( $I_D$ ) is a result of the capacitance of the junction in dynamic situations. The capacitance depends on junction type and size. Hence the total current will be given by the equation:

$$I(t) = I_S(t) + I_D(t) + I_F(t) + I_N(t).$$

(2.7)

Another model, the nonlinear-resistive junction (RSJN) model is similar to the RSJ model, except that the normal current component is approximated by the following piecewise-linear expression:

$$I_{N} = \begin{cases} G_{L}V & \text{for } |V| < V_{g} \\ G_{N}V & \text{for } |V| > V_{g} \end{cases}$$

(2.8)

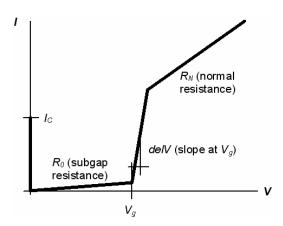

where  $G_L$  is a leakage conductance that characterizes the subgap leakage current [10]. The circuit simulator used for our research was JSIM [13], a simulator developed at Berkeley University, which has been adapted for Windows at the University of Twente. The junction model used by JSIM is similar to the RSJN model. The junctions are described using the piece-wise linear curve of Figure 2.3. In this model the subgap resistance is indicated as  $R_0$  and the normal resistance as  $R_N$ . In the JSIM model, the slope of the R-branch at the gap voltage  $V_g$  can be modelled using the delV parameter. The junction capacitance is not shown in the figure, but can be entered separately. Furthermore, it is possible to model the magnetic field dependence of the critical current. A more detailed treatment can be found in [1], [10], [14].

Figure 2.3: Piece-wise linear model of a JJ in the SPICE-based simulator JSIM.

#### 2.3 Josephson Junction Circuits

The recognition of the advantages of superconductor integrated circuits has motivated several attempts to develop a practical Josephson junction digital technology, among them, the large-scale IBM supercomputer project (1969 – 1983) [15] and the MITI (Ministry of International Trade and Industry) project in Japan (1981-1990) [16] are worth mentioning. These projects were responsible for several important contributions to SCE. However, they were terminated without commercialization of the technology because the achieved circuit speed, a clock frequency of around 1 GHz in 1990, was only marginally higher than that of the fastest contemporary semiconductor transistor circuits (GaAs), and could not justify the necessary Helium cooling. The main factor limiting the speed was the unfortunate choice of the so-called latching (or "voltage-state") circuitry based on the properties of unshunted JJs as explained later. Furthermore, the Lead alloy technology used for the realisation of JJs had thermal cycling problems.

As can be shown from equations (2.4) and (2.7), such unshunted JJs, if biased with a DC current within the range  $-I_C < I < +I_C$ , have two different states: a superconducting state with vanishing voltage drop V across the junction, and a resistive state with  $|V| \approx V_g = 2\Delta(T)/e$ . In latching logic, the superconducting state is used to denote a binary "0", while the resistive state represents binary "1". A switching from "0" to "1" is rather fast; a few picoseconds for junctions with high critical current density,  $J_C$  of a few kA/cm². However, the reciprocal switching ("1" $\rightarrow$ "0") is much more complex and is long, in the order of one nanosecond, to avoid errors. This is due to the fact that the reset cannot be achieved by merely turning the signal off as the circuit will remain in its "1" state and hence the name latching logic. The only practical way to get the state to "0" is to switch off the bias current. This is achieved by using AC rather than a DC current supply of all the gates. This is essentially the price which was paid for an attempt to mimic the information

representation by a DC voltage, which is the preferred option in semiconductor electronics, but is very unnatural for superconductors with their macroscopic quantum dynamics.

From the practical point of view, another problem of latching logic was even more drastic. Most latching devices must be driven by an external clock signal which also provides the necessary power. The total current needed to run a VLSI circuit could reach many amperes, and feeding integrated circuits with such huge currents at multi-GHz frequencies would create severe crosstalk between the off-chip segments of AC power and signal lines.

An alternative approach to use superconductors for computing is based on their natural property to quantize the magnetic flux,  $\Phi$ . The flux through an element of area (A) perpendicular to the direction of magnetic field (B) is given by the product of the magnetic field density and the area elements:

$$\Phi = \int B_n \cdot dA \tag{2.9}$$

through any closed superconducting loop in multiples of the flux quantum  $\Phi_0$ , ( $\Phi = n \cdot \Phi_0$ ). On substituting equation (2.4) written for two end points of an almost closed loop into Faraday's induction law for this loop results in:

$$\frac{d\Phi}{dt} = V \tag{2.10}$$

and integration of the resulting equation over time yields the relation between the magnetic flux and Josephson phase difference,  $\phi$ :

$$\phi = 2\pi \frac{\Phi}{\Phi_0}.\tag{2.11}$$

Due to the relation (2.11), the variable  $\Phi(r, t) = (\Phi_0/2\pi)$ .  $\phi(r, t)$  is frequently referred to as "flux" in a given point of the circuit, where  $\psi(r,t) = |\psi| \exp\{i\phi(r,t)\}$  is the wave function describing the superconductor of amplitude  $|\psi|$ , even if it does not belong to any specific superconductor loop [2]. On a closed loop, it requires that the wavefunctions in these two (now identical) points coincide, besides there maybe a phase difference multiple of  $2\pi$ . Then equation 2.11 yields the flux quantization:

$$\Phi = n \cdot \Phi_o; \qquad n = 0, \pm 1, \pm 2, \dots \tag{2.12}$$

Recently, it was found that it is possible to fabricate and study so-called Josephson  $\pi$ -junctions having a ground state where the phases of the superconducting wave functions in the two electrodes differ only by  $\pi$ . The most interesting phenomena take place when one considers a long Josephson junction one part of which behaves as a conventional 0-junction and another part as a  $\pi$ -junction. There are several available technologies to fabricate such devices. At the boundary between 0 and  $\pi$  regions a new type of vortex (a

semifluxon) carrying only half of a flux quantum can form spontaneously. For more detailed treatment see [17], [18].

Evidently, digital information can be coded by certain values of the integer n, for example, the flux states with n=0 and n=1 may be used to represent binary zero and one, respectively. If a superconducting loop is made of a bulk superconductor, switching between the different flux states requires the suppression and restoration of superconductivity in at least some cross-section of the loop; the latter process would take much time,  $\sim 100$  ps for Nb JJs. However, if the loop is interrupted with a JJ, switching can be performed much faster, for Nb-based junctions, actually in a fraction of a picosecond.

The basic idea of these devices is to use transient dynamics for information transfer. According to Faraday's induction law in equation (2.10), during the switching between the neighbouring flux states a short voltage pulse is formed across the junction. Since for SFQ circuits the flux change is quantised ( $\Delta\Phi \approx \Phi_0$ ), the pulse area is also quantised:

$$\int V(t) dt = \Phi_0 = 2mV \cdot ps \tag{2.13}$$

For typical, critically shunted Josephson junctions, the FWHM (Full-Width Half-Maximum) switching time is in the order of  $4\tau_0$ , (i.e. a few picoseconds) where  $\tau_0$  is the transient time constant given by the expression  $\tau_0 = RC = (\Phi_0 C / 2\pi I_C)^{1/2}$  [2]. The amplitude of the pulse  $V_{max} = \Phi_0/4\tau_0 = 1.5~I_CR$  is in the order of a millivolt. In dynamic SFQ circuits these "SFQ pulses" are passed to other devices along either passive superconductor transmission lines or, if current/power gain is needed, active JTLs (Josephson Transmission Lines). Dynamic SFQ circuits are very attractive because the pulses can be naturally generated, reproduced/recovered, memorized and processed with simple SFQ devices whose speed is much higher and energy dissipation much smaller than that of the latching logic. Another feature which distinguishes dynamic SFQ circuits from other logic families using two-terminal devices is the pulsed nature of the signals. For such picosecond signals, even an inductance of a few pH may provide a substantial isolation between the circuit input and output. For conventional signals such as voltage steps in semiconductor electronics, three-terminal devices like transistors are very essential to provide sufficient isolation. In contrast, RSFQ circuits with their return-to-zero signals are quite robust despite using just two-terminal JJ devices, eliminating the need for superconductor transistors.

All RSFQ circuits can be divided into two groups:

- a) asynchronous components with no internal memory, which generate an output SFQ pulse immediately upon the arrival of an input pulse,

- b) synchronous (clocked) circuits with internal memory, where the generation of an output pulse may be delayed substantially after the arrival of data SFQ pulse(s), until the arrival of one more SFQ pulse playing the role of clock signal.

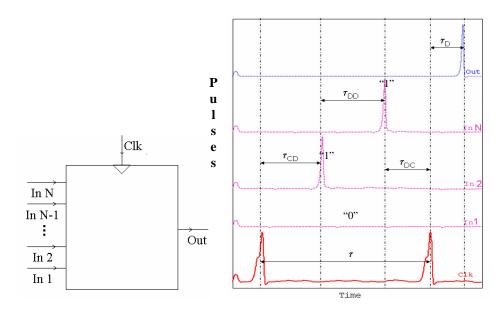

Figure 2.4: Protocol for RSFQ circuits: a) arbitrary logic block and b) timing parameters (not to scale).

b)

Examples of the first group are the JTL, Splitter, Merger [7] etc. while AND logic gate, OR logic gate etc. belongs to the second group. The signalling protocol in RSFQ circuits have to be defined as it differs from that in conventional combinational logic as accepted in semiconductor electronics, because of the following two inter-related factors:

- "return-to-zero" nature of SFQ pulses,

- natural internal memory of quantizing SFQ loops.

Most RSFQ circuits implemented so far have been based on the standard RSFQ protocol illustrated schematically in Figure 2.4. An N-input logic box is given as example in Figure 2.4a. In this system, a signal in a data line is treated as binary "1" if it carries an SFQ pulse within the given clock period (signal "In 2" and "In N" in Figure 2.4b). The absence of the pulse during this time interval (signal "In 1" in Figure 2.4b) is interpreted as binary "0". More generally, any RSFQ circuit using this protocol can be considered as a connection of asynchronous components and clocked gates ("elementary cells" or "logic latches"). Such a gate has a few (typically two) internal states and may be functionally considered as an explicit or implicit integration of combinational logic and a latch. Input SFQ pulses change the state of the latch which stores this information until the arrival of the clock pulse. This pulse triggers output signal(s) and resets the cell into its initial state. As evident from Figure 2.4b, clocked flip-flops and logic gates cannot be fully characterized (as asynchronous components) by just the delay  $\tau_D$  between the input (in this case clock) pulse and the output pulse; at least three more time constants have to be included:

- $\tau_{CD}$  or clock-to-data interval; the minimum value of the interval between the clock pulse and the first data pulse ("In 2" in Figure 2.4b),

- $\tau_{DD}$  or data-to-data interval; the minimum value(s) of the interval(s) between the data pulses,

- $\tau_{DC}$  or data-to-clock interval; the minimum value of the interval between the last of the data pulses ("In N" in Figure 2.4b) and the next clock pulse, at which the device operates correctly.

Since the sum  $\tau_{CD} + \tau_{DD} + \tau_{DC}$  defines the clock period, its minimum value determines the maximum clock frequency of the gate given by:

$$(f_c)_{\text{max}} = \frac{1}{(\tau_{cD} + \tau_{DC} + \tau_{DC})_{\text{min}}}$$

(2.14)

In all single-input gates, such as an inverter, the data-to-data interval is not defined. Moreover, some two-input gates, like the AND and XOR operate at an arbitrary data-to-data interval  $\tau_{DD}$ . In these cases, the  $(\tau_{DD})_{min}$  can be ignored and is set to 0 for calculations.

#### 2.4 Design and Implementation of RSFQ Circuits

One of the primary problems in the development of large RSFQ circuits was the lack of appropriate design methodologies that effectively utilize computer-aided design (CAD) tools while providing direction for the development of new tools specific to this superconducting technology. It is debatable whether RSFQ circuits should be designed based on leveraging techniques developed for semiconductor circuits or whether completely new methodologies specific to RSFQ logic should be created. The proponents of the former approach affirm the analogies between both technologies, particularly strong at the system level, and stress the achievements and maturity of semiconductor technologies. The proponents of the latter approach stress the substantial differences between the two technologies, particularly strong at the circuit level, and the large difference in the operating speed, power consumption, and fabrication process. A combination of both strategies is probably the most effective methodology.

The design methodology for small-scale RSFQ circuits is centred around circuit simulation and the optimization of device parameters while the design methodology for large-scale circuits is focused on logic (gate-level) simulation and optimization of the interconnect delays within the circuit. The second important feature is the development of libraries composing of basic RSFQ cells, permitting the design of circuits of arbitrary complexity. This process of constructing large RSFQ circuits out of a general family of primitive gates has not been commonly accepted. The main obstacles with regard to this approach are:

• difficulty of isolating RSFQ gates from each other;

- large uncertainty of delays and other timing parameters of RSFQ cells due to variations in the fabrication process and changes in the bias currents;

- use of Josephson transmission lines (JTLs) for interconnects;

- low fan-out of RSFQ gates;

- lack of a well-established methodology for modelling the timing of RSFQ circuits;

- lack of tools for the timing analysis and timing optimization of RSFQ circuits;

- lack of tools to logically simulate RSFQ circuits.

The latter three obstacles are being dealt with by modifying and integrating the advanced CAD tools for semiconductors. The design of large RSFQ circuits is currently based almost exclusively on a full-custom methodology. This approach is justified by the immature state of RSFQ technology and by the niche applications of RSFQ circuits, such as time-to-digital converters [19] or decimation filters for analogue-to-digital converters [20], where the advantages in performance, in terms of both speed and power, are of primary importance. Nevertheless, this design style also leads to long design times and significant design effort. Further development of RSFQ technology and its application to digital signal processing [21] and general purpose computing [22], [23] requires adopting a more labour efficient and less error-prone semicustom design methodology. Unfortunately, differences between superconducting RSFQ logic and traditional semiconductor technologies prevent the direct application of semiconductor methods and tools to the automated design of RSFQ circuits.

The design flow of a small-scale RSFQ circuit consists of three main phases: synthesis of the circuit structure, optimization of the circuit parameters, and physical implementation of the circuit layout. This design flow is commonly accepted and supported by multiple commercial and public domain CAD tools [24], [25].

The synthesis of a small-scale RSFQ circuit begins with a description of the circuit function using a Mealy state transition diagram or present-state/next-state table. The circuit structure along with a set of near exhaustive input stimuli is used to verify the functional behaviour of the circuit which is derived from the circuit function. This step is currently not automated and is primarily dependent on the intuition of the designer. The circuit is simulated and modified iteratively to verify full functionality for all input sequences.

The custom optimization package is then used to determine the optimal nominal values of the circuit device parameters that achieve the maximum yield in case of parametric variation during realisation [26]. Before the optimization procedure can begin, a pass–fail criterion is generated to permit distinguishing between sets of operating parameters that give correct and incorrect circuit functionality. These criteria are generated automatically by simulating the circuit for the set of initial operating parameters. This pass–fail criterion only considers the externally observed behaviour of the circuit, i.e. sequences of pulses at the inputs and outputs of the cell.

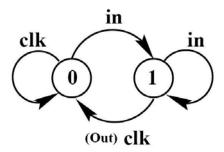

Figure 2.5: Mealy diagram for an RSFQ DFF.

After the optimum values of the device parameters are determined, the layout view of the cell has to be drawn manually. At this level of abstraction, the circuit is described in terms of the physical geometric data used to produce the individual lithographic masks. The layout data is then compared with the schematic and further fine tuning is carried out taking into account the parasitics. The next sub-section will illustrate the process using an RSFQ circuit example.

#### 2.4.1 An RSFQ DFF

An RSFQ DFF, being a simple circuit, is used here as a design example. The Mealy state diagram for the RSFQ DFF is shown in Figure 2.5. If the circuit is in its "0" state, arrival of the "in" pulse will set the DFF to its "1" state. Arrival of a "clk" pulse at this state will release an SFQ pulse to the output of the circuit (shown in the brackets) and resets the DFF back to the "0" state. If a "clk" pulse arrives in the "0" state or if an "in" pulse arrives if it is in the "1" state, the DFF circuit will remain in its original state.

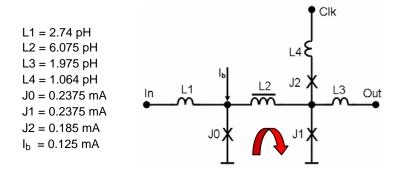

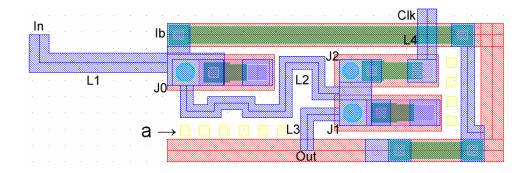

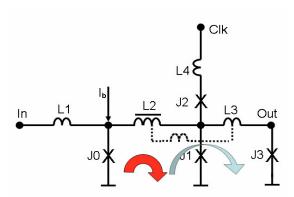

Figure 2.6: An RSFQ D-type Flip-flop with optimised circuit parameters.

The circuit schematic of the DFF is shown in Figure 2.6. It consists of three JJs (J0-J2), 4 inductors (L1-L4) and a bias current source, I<sub>b</sub>. The storage inductor L2 (inductor with a line over it) forms the storage loop with J0 and J1 (shown by the arrow). The JJs, J1 and J2 form the decision-making pair in the circuit. This circuit has been optimised at Chalmers University in Sweden [27] for the HYPRES Nb process described in the fourth chapter of this thesis. The maximum frequency of operation is 20 GHz at a temperature of 4 K.

The operation of an RSFQ DFF is as follows. Arrival of an SFQ pulse at the "In" node will switch the junction J0 and a magnetic flux quantum (fluxon) is stored in the loop containing L2. Arrival of a pulse at the "Clk" node will switch either J1 or J2 depending on the state of the storage loop. The critical currents of J1 and J2 are designed such that if a fluxon is present in the storage loop, J1 will be switched releasing the stored fluxon to the "Out" node. If a fluxon is not stored in the loop, J2 will be switched instead of J1 and there will be no emission of a fluxon to the "Out" node.